# Digital Electronics

# Eighth Edition

# Digital Electronics Principles and Applications

Roger Tokheim

#### DIGITAL ELECTRONICS: PRINCIPLES AND APPLICATIONS, EIGHTH EDITION

Published by McGraw-Hill, a business unit of The McGraw-Hill Companies, Inc., 1221 Avenue of the Americas, New York, NY, 10020. Copyright © 2014 by The McGraw-Hill Companies, Inc. All rights reserved. Printed in the United States of America. Previous editions © 2008, 2003, and 1999. No part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written consent of The McGraw-Hill Companies, Inc., including, but not limited to, in any network or other electronic storage or transmission, or broadcast for distance learning.

Some ancillaries, including electronic and print components, may not be available to customers outside the United States.

This book is printed on acid-free paper.

1234567890QVR/QVR109876543

ISBN 978-125-906092-2 MHID 125-906092-6

All credits appearing on page or at the end of the book are considered to be an extension of the copyright page.

The Internet addresses listed in the text were accurate at the time of publication. The inclusion of a website does not indicate an endorsement by the authors or McGraw-Hill, and McGraw-Hill does not guarantee the accuracy of the information presented at these sites.

# Contents

3-10

3-11

3 - 12

3-13

3-14

3-15

3-16

4-1

4-2

4-3

4-4

4-5

4-6

4-7

4-8

4-9

4-10

4-11

4-12

4-13

4-14

4-15

4-16

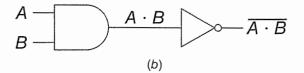

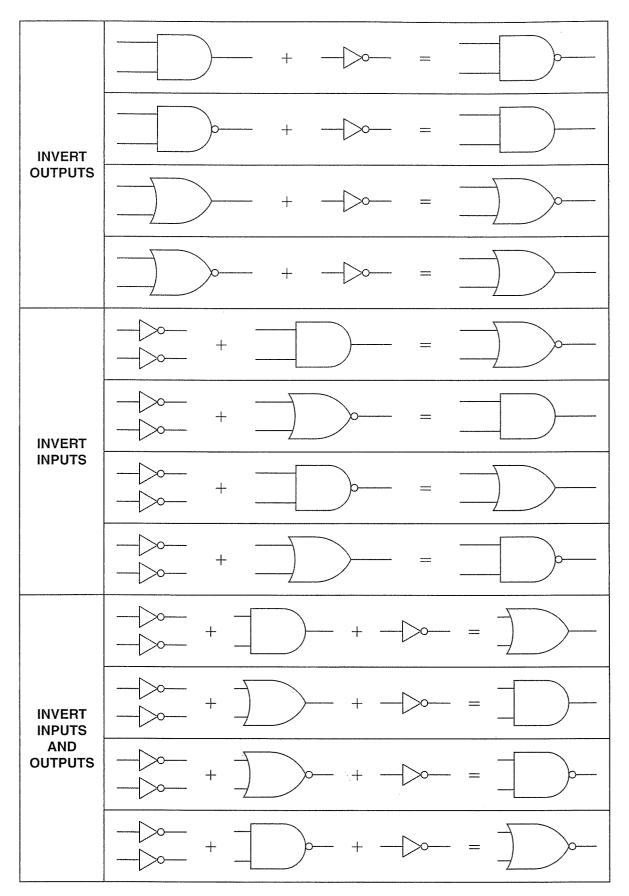

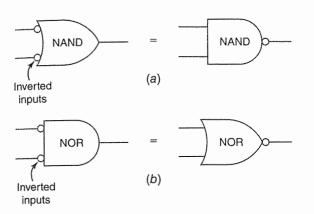

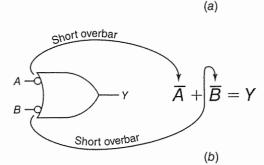

Using Inverters to Convert Gates ..... 59

Troubleshooting Simple Gate Circuits ..... 69

IEEE Logic Symbols ..... 72

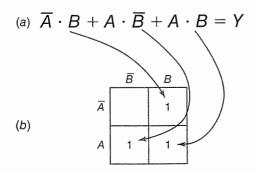

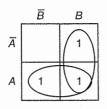

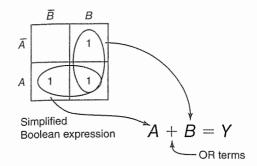

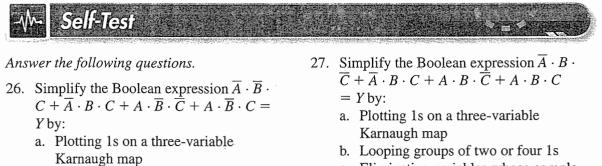

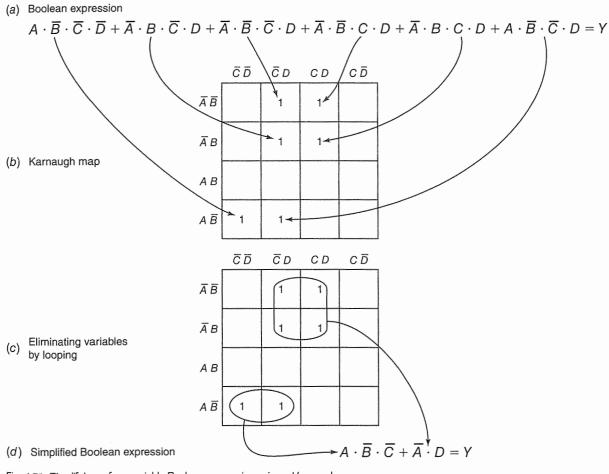

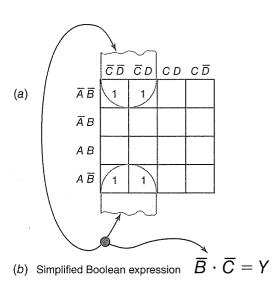

Simplifying Boolean Expressions. . . . . . . . 99

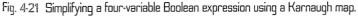

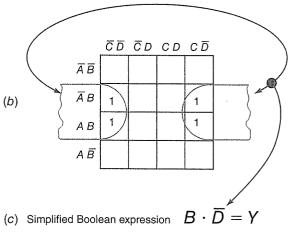

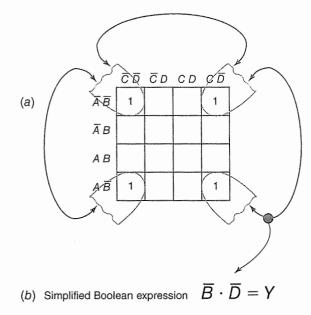

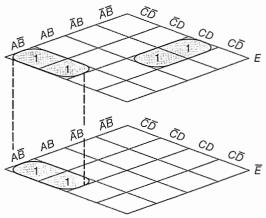

Karnaugh Maps..... 100

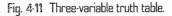

Karnaugh Maps with Three Variables. . . . . 101

Karnaugh Maps with Four Variables ..... 103

More Karnaugh Maps..... 104

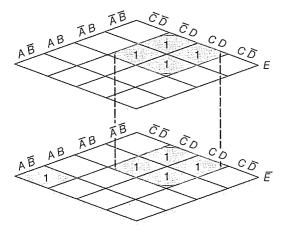

A Five-Variable Karnaugh Map ..... 105

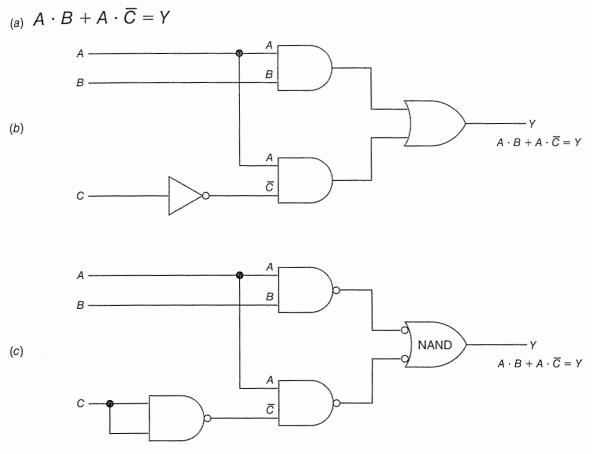

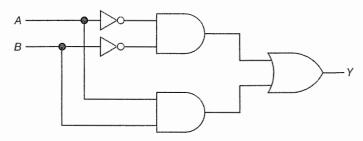

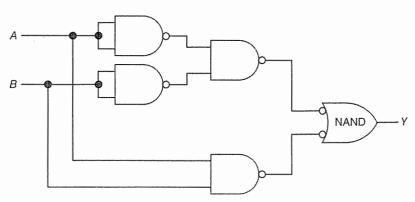

Using NAND Logic ..... 106

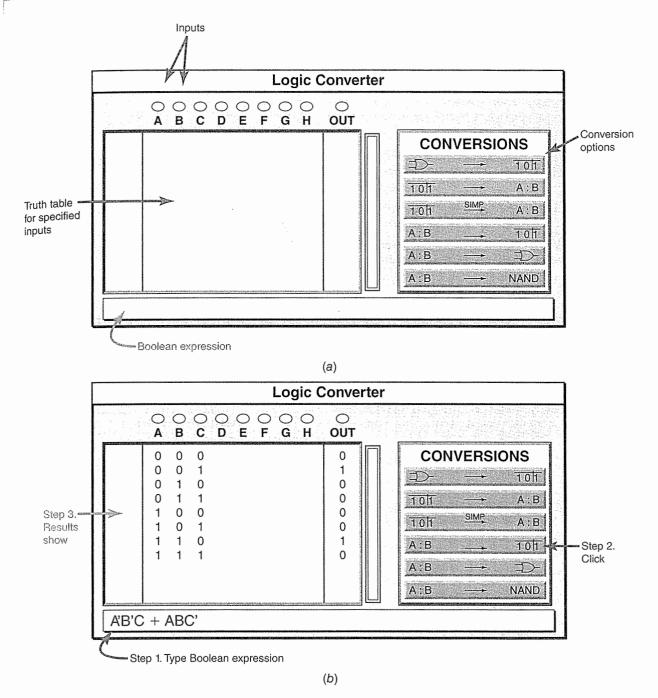

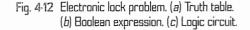

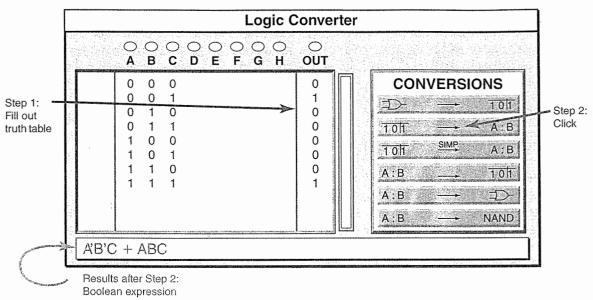

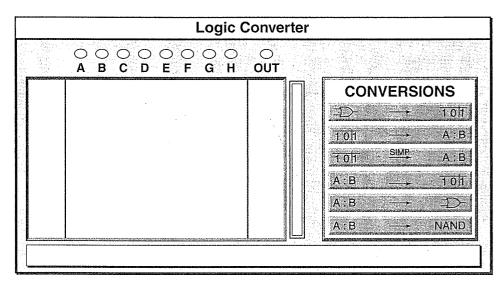

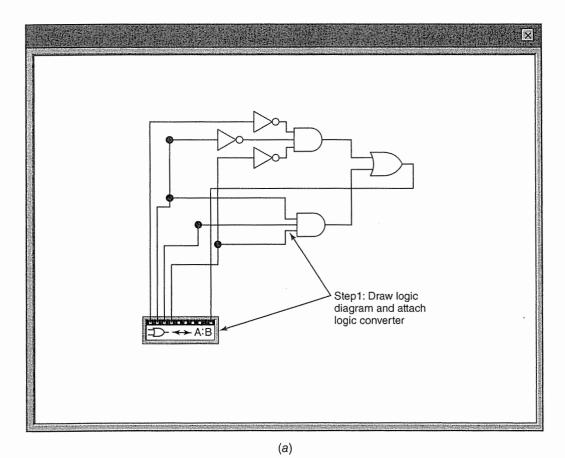

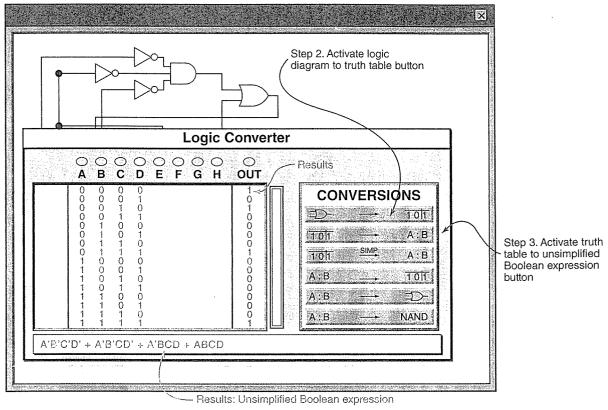

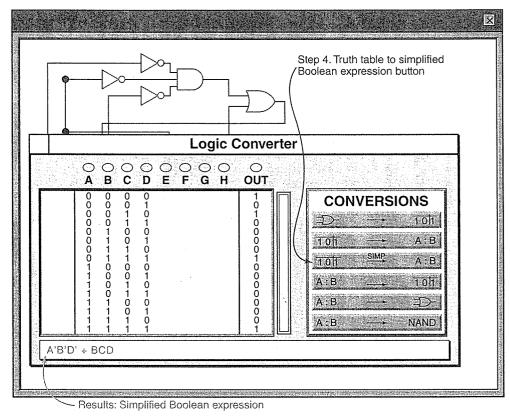

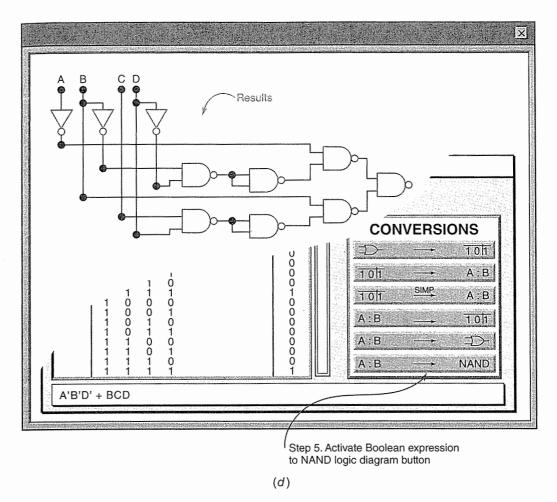

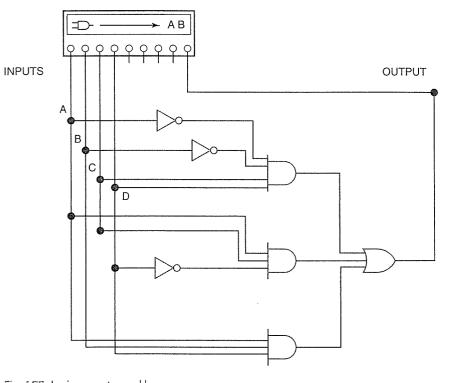

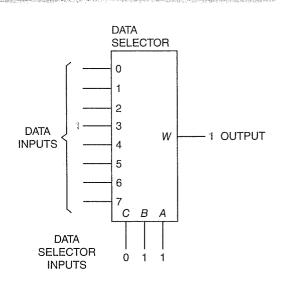

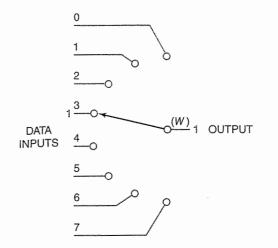

Computer Simulations: Logic Converter ... 108

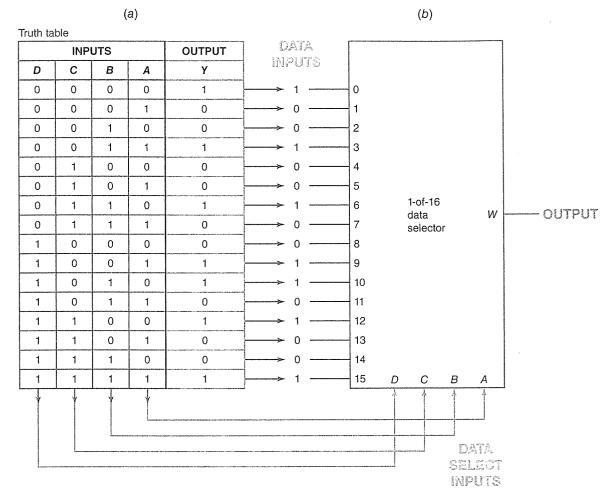

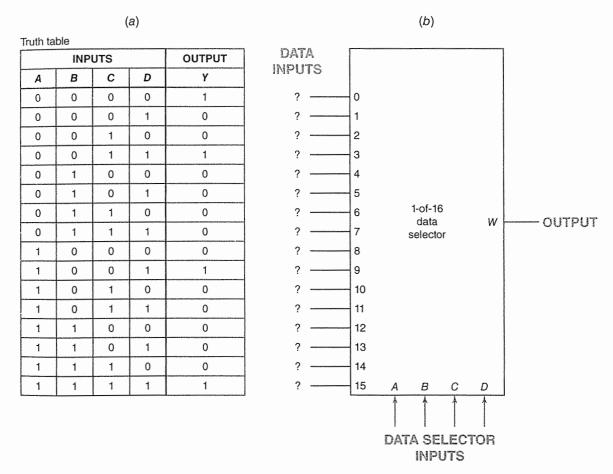

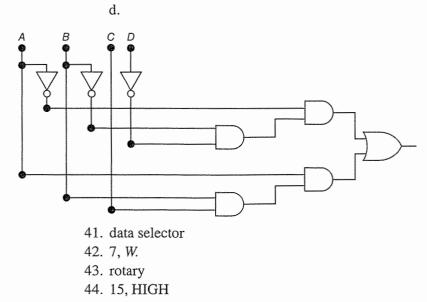

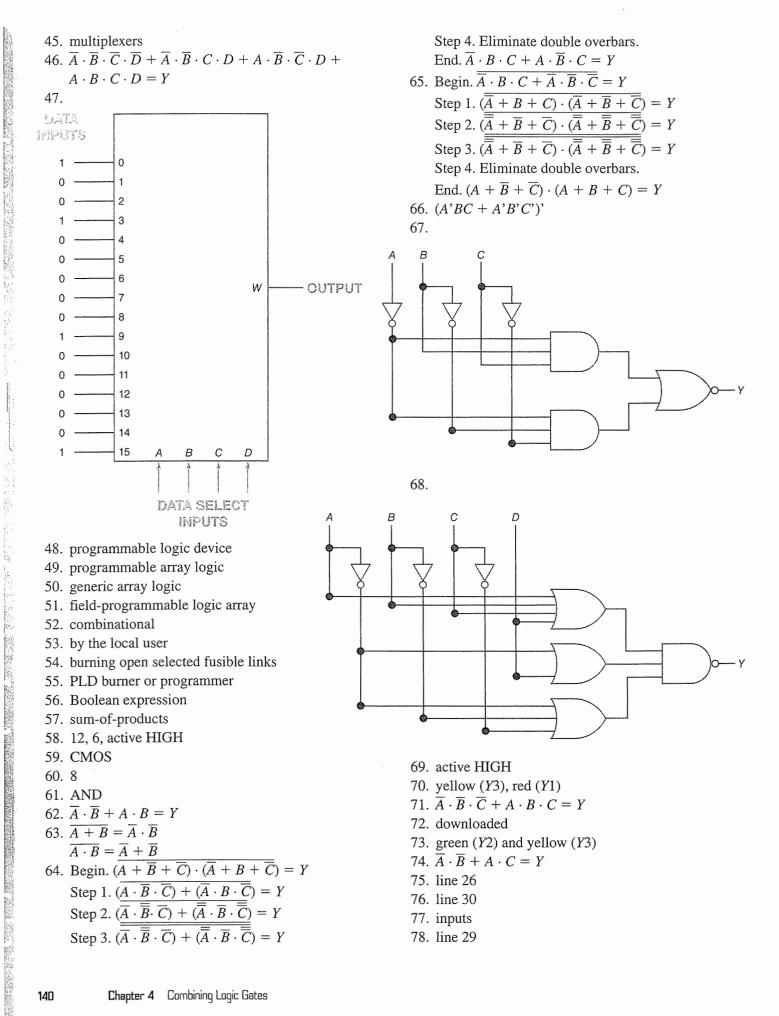

Solving Logic Problems: Data Selectors ... 112

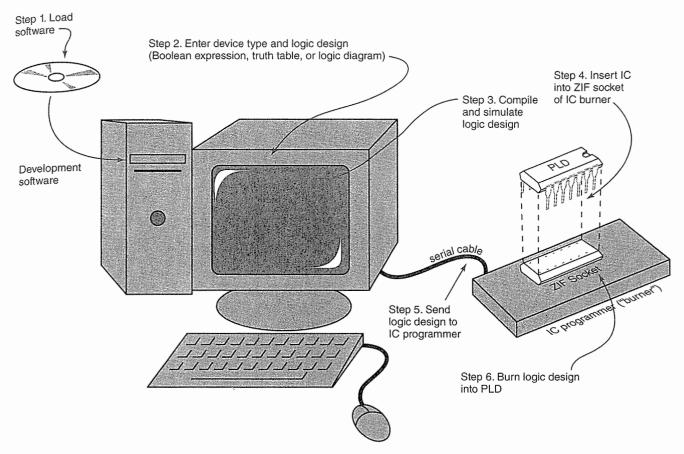

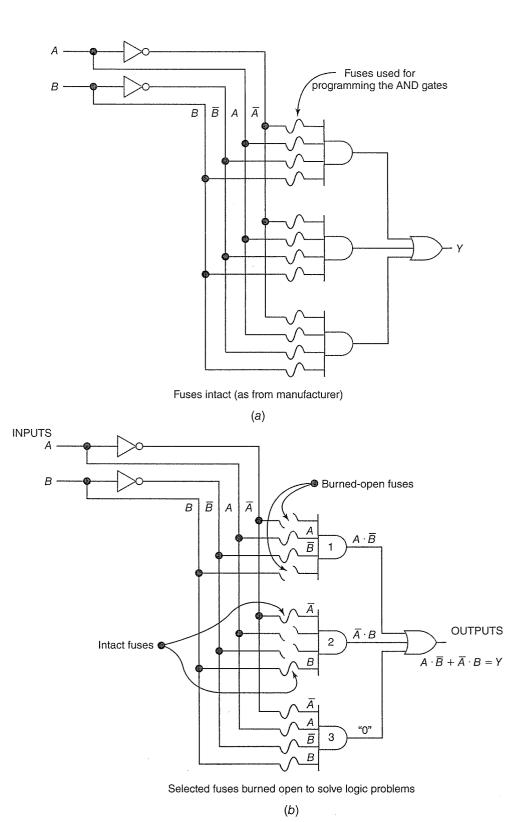

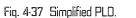

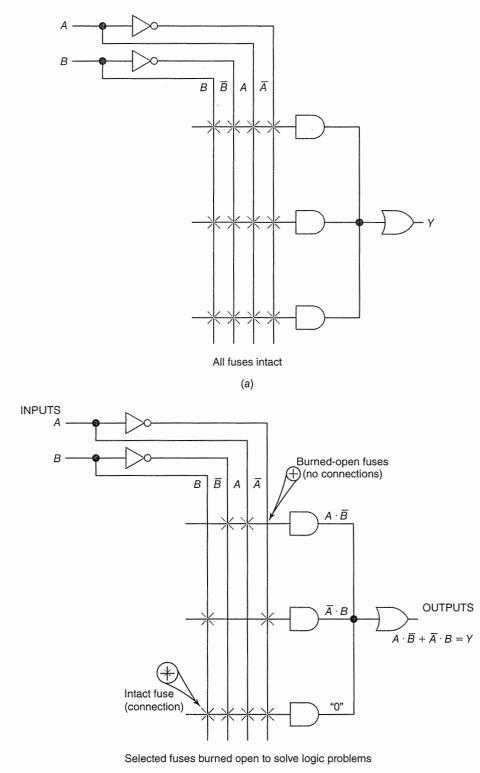

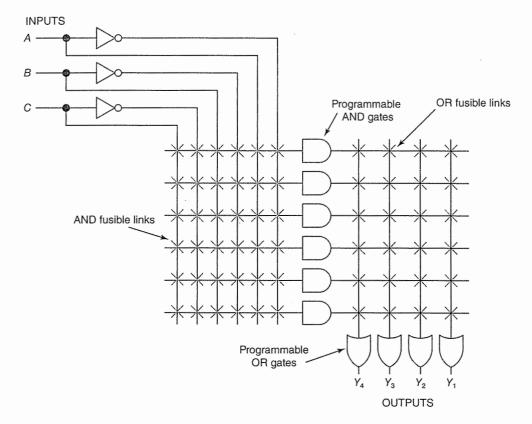

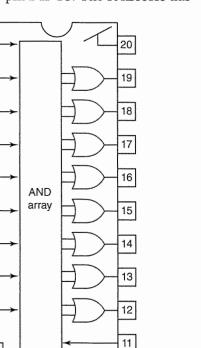

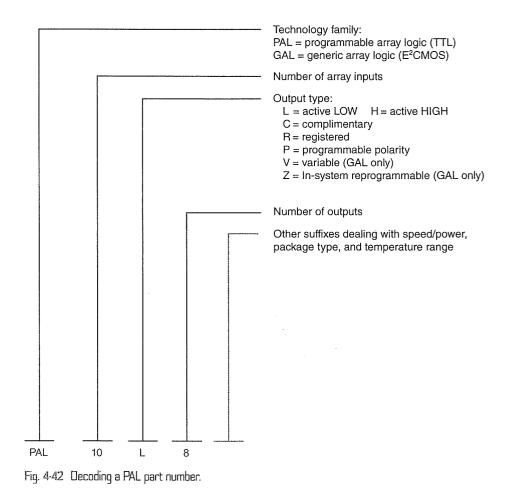

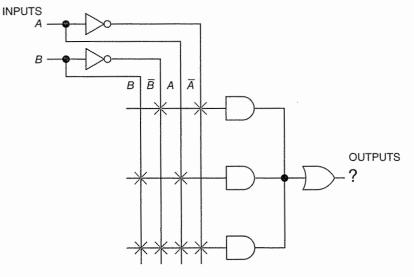

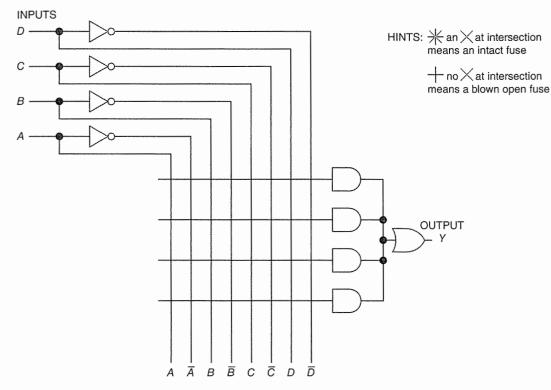

Programmable Logic Devices (PLDs) .... 116

Using De Morgan's Theorems ..... 124

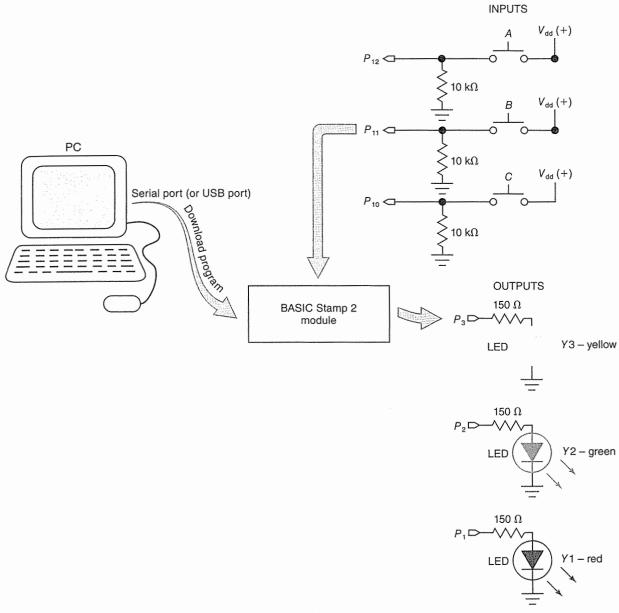

Solving a Logic Problem (BASIC Stamp

Answers to Self-Tests ..... 136

Chapter 5 IC Specifications and Simple Interfacing

Logic Functions Using Software

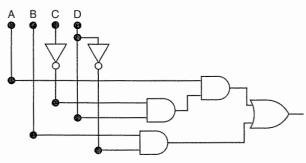

Chapter 4 Combining Logic Gates

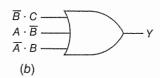

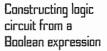

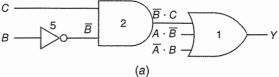

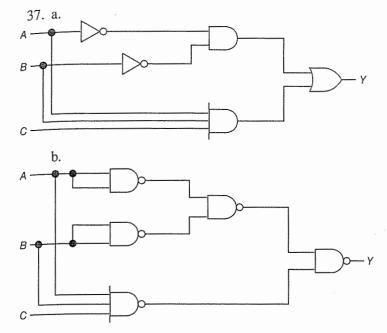

Constructing Circuits from

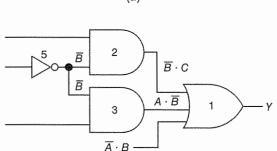

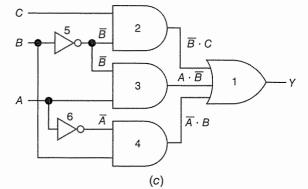

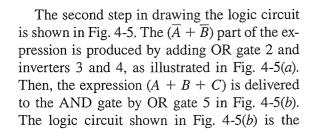

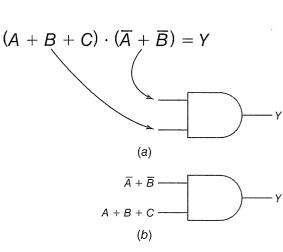

Drawing a Circuit from a Maxterm

|                                                                                                                  | s Foreword                                                                                                                                                                                                                                                                                                                       |                                                                                  |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|                                                                                                                  | •••••••••••••••••••••••••••••••••••••••                                                                                                                                                                                                                                                                                          |                                                                                  |

|                                                                                                                  | wledgments                                                                                                                                                                                                                                                                                                                       |                                                                                  |

|                                                                                                                  | rough                                                                                                                                                                                                                                                                                                                            |                                                                                  |

|                                                                                                                  | the Author                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| Safety.                                                                                                          |                                                                                                                                                                                                                                                                                                                                  | xv                                                                               |

| Chapter                                                                                                          | 1 Digital Electronics                                                                                                                                                                                                                                                                                                            | 1                                                                                |

| 1-1                                                                                                              | What Is a Digital Signal?                                                                                                                                                                                                                                                                                                        | . 2                                                                              |

| 1-2                                                                                                              | Why Use Digital Circuits?                                                                                                                                                                                                                                                                                                        | . 4                                                                              |

| 1-3                                                                                                              | Where Are Digital Circuits Used?                                                                                                                                                                                                                                                                                                 | . 7                                                                              |

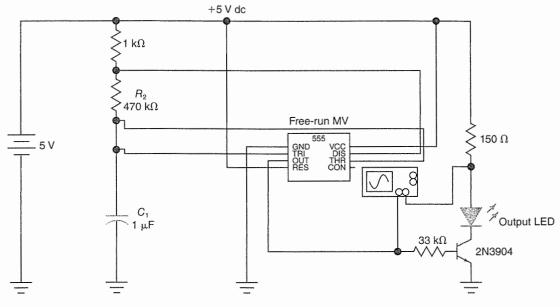

| 1-4                                                                                                              | How Do You Generate a Digital Signal?                                                                                                                                                                                                                                                                                            |                                                                                  |

| 1-5                                                                                                              | How Do You Test for a Digital Signal?                                                                                                                                                                                                                                                                                            | 15                                                                               |

| 1-6                                                                                                              | Simple Instruments                                                                                                                                                                                                                                                                                                               |                                                                                  |

| Summa                                                                                                            | ury                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|                                                                                                                  | Review Questions                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|                                                                                                                  | Thinking Questions                                                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                  | rs to Self-Tests                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| Chapter                                                                                                          | 2 Numbers We Use in Digital Electronics                                                                                                                                                                                                                                                                                          | 27                                                                               |

|                                                                                                                  |                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

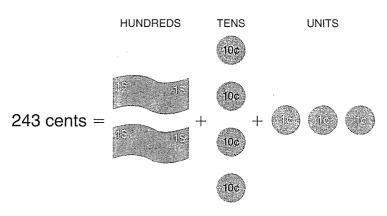

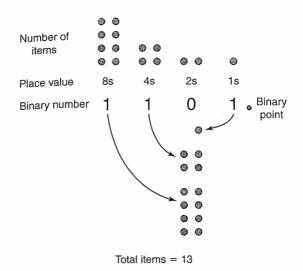

| 2-1                                                                                                              | Counting in Decimal and Binary                                                                                                                                                                                                                                                                                                   | 27                                                                               |

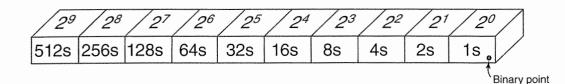

| 2-1<br>2-2                                                                                                       | Counting in Decimal and Binary<br>Place Value                                                                                                                                                                                                                                                                                    |                                                                                  |

|                                                                                                                  |                                                                                                                                                                                                                                                                                                                                  | 28                                                                               |

| 2-2                                                                                                              | Place Value                                                                                                                                                                                                                                                                                                                      | 28<br>30                                                                         |

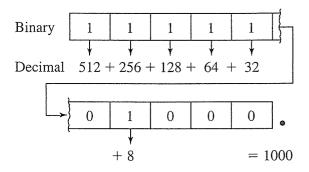

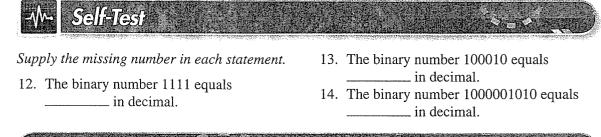

| 2-2<br>2-3                                                                                                       | Place Value<br>Binary to Decimal Conversion                                                                                                                                                                                                                                                                                      | 28<br>30<br>30                                                                   |

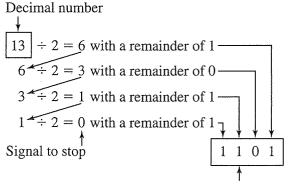

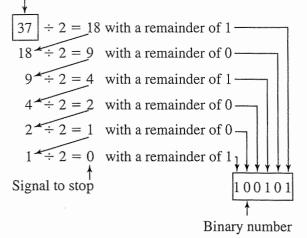

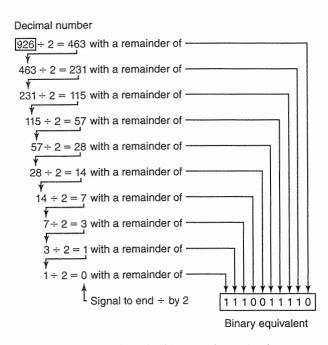

| 2-2<br>2-3<br>2-4                                                                                                | Place Value<br>Binary to Decimal Conversion<br>Decimal to Binary Conversion                                                                                                                                                                                                                                                      | 28<br>30<br>30<br>31                                                             |

| 2-2<br>2-3<br>2-4<br>2-5                                                                                         | Place ValueBinary to Decimal ConversionDecimal to Binary ConversionElectronic Translators                                                                                                                                                                                                                                        | 28<br>30<br>30<br>31<br>34                                                       |

| 2-2<br>2-3<br>2-4<br>2-5<br>2-6                                                                                  | Place ValueBinary to Decimal ConversionDecimal to Binary ConversionElectronic TranslatorsHexadecimal Numbers                                                                                                                                                                                                                     | 28<br>30<br>30<br>31<br>34<br>36                                                 |

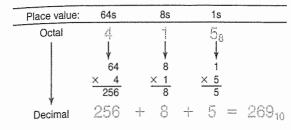

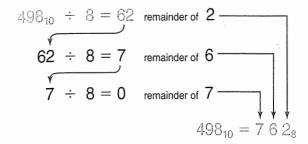

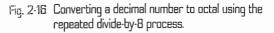

| 2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8                                                                    | Place ValueBinary to Decimal ConversionDecimal to Binary ConversionElectronic TranslatorsHexadecimal NumbersOctal Numbers                                                                                                                                                                                                        | 28<br>30<br>30<br>31<br>34<br>36<br>37                                           |

| 2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>Summa                                                           | Place ValueBinary to Decimal ConversionDecimal to Binary ConversionElectronic TranslatorsHexadecimal NumbersOctal NumbersBits, Bytes, Nibbles and Word Size                                                                                                                                                                      | 28<br>30<br>31<br>34<br>36<br>37<br>39                                           |

| 2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>Summa<br>Chapter                                                | Place ValueBinary to Decimal ConversionDecimal to Binary ConversionElectronic TranslatorsHexadecimal NumbersOctal NumbersBits, Bytes, Nibbles and Word Sizeury                                                                                                                                                                   | 28<br>30<br>31<br>34<br>36<br>37<br>39<br>39                                     |

| 2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>Summa<br>Chapter<br>Critical                                    | Place Value<br>Binary to Decimal Conversion<br>Decimal to Binary Conversion<br>Electronic Translators<br>Hexadecimal Numbers<br>Octal Numbers<br>Bits, Bytes, Nibbles and Word Size<br>ry<br>r Review Questions                                                                                                                  | 28<br>30<br>31<br>34<br>36<br>37<br>39<br>39<br>40                               |

| 2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>Summa<br>Chapter<br>Critical<br>Answer                          | Place Value                                                                                                                                                                                                                                                                                                                      | 28<br>30<br>31<br>34<br>36<br>37<br>39<br>39<br>40                               |

| 2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>Summa<br>Chapter<br>Critical<br>Answer                          | Place ValueBinary to Decimal ConversionDecimal to Binary ConversionElectronic TranslatorsHexadecimal NumbersOctal NumbersBits, Bytes, Nibbles and Word Sizeryr Review QuestionsThinking Questionsrs to Self-Tests- 3 Logic Gates                                                                                                 | 28<br>30<br>31<br>34<br>36<br>37<br>39<br>39<br>40<br>42<br>43                   |

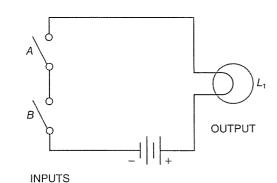

| 2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>Summa<br>Chapter<br>Critical<br>Answer<br>Chapter<br>3-1        | Place Value<br>Binary to Decimal Conversion<br>Decimal to Binary Conversion<br>Electronic Translators<br>Hexadecimal Numbers<br>Octal Numbers<br>Bits, Bytes, Nibbles and Word Size<br>Bits, Bytes, Nibbles and Word Size<br>ry<br>r Review Questions<br>Thinking Questions<br>st to Self-Tests<br>3 Logic Gates<br>The AND Gate | 28<br>30<br>31<br>34<br>36<br>37<br>39<br>39<br>40<br>42<br>42<br>43             |

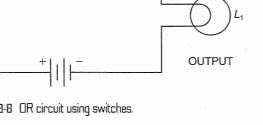

| 2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>Summa<br>Chapter<br>Critical<br>Answer<br>Chapter<br>3-1<br>3-2 | Place ValueBinary to Decimal ConversionDecimal to Binary ConversionElectronic TranslatorsHexadecimal NumbersOctal NumbersBits, Bytes, Nibbles and Word Sizeuryr Review QuestionsThinking Questionsrs to Self-Tests-3 Logic GatesThe AND GateThe OR Gate                                                                          | 28<br>30<br>30<br>31<br>34<br>36<br>37<br>39<br>39<br>40<br>42<br>43<br>43<br>46 |

| 2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>Summa<br>Chapter<br>Critical<br>Answer<br>Chapter<br>3-1        | Place Value<br>Binary to Decimal Conversion<br>Decimal to Binary Conversion<br>Electronic Translators<br>Hexadecimal Numbers<br>Octal Numbers<br>Bits, Bytes, Nibbles and Word Size<br>Bits, Bytes, Nibbles and Word Size<br>ry<br>r Review Questions<br>Thinking Questions<br>st to Self-Tests<br>3 Logic Gates<br>The AND Gate | 28<br>30<br>30<br>31<br>34<br>36<br>37<br>39<br>40<br>42<br>43<br>43<br>46<br>48 |

3-6

3-7

3-8

3-9

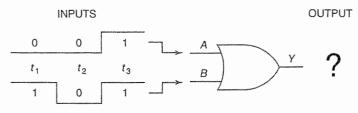

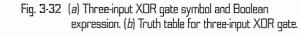

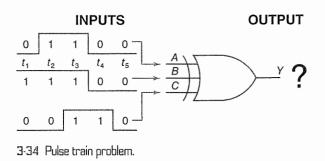

The Exclusive OR Gate

| The Exclusive OR Gate                |     |                                 |     |

|--------------------------------------|-----|---------------------------------|-----|

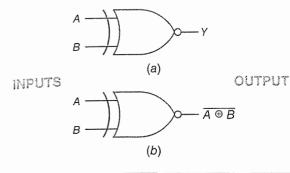

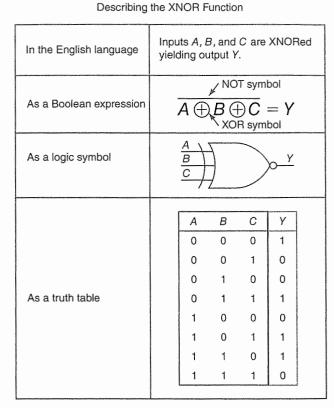

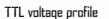

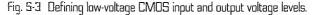

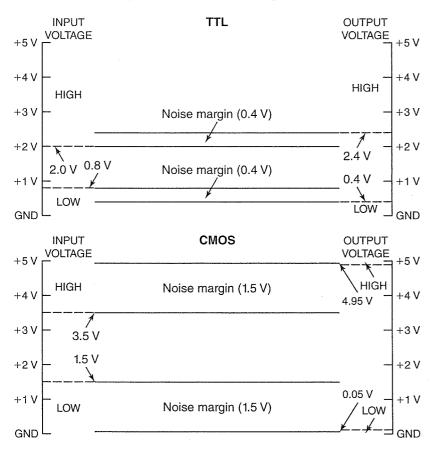

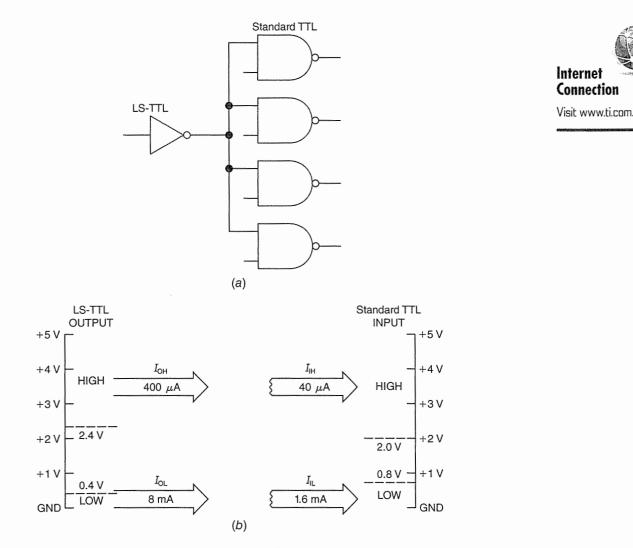

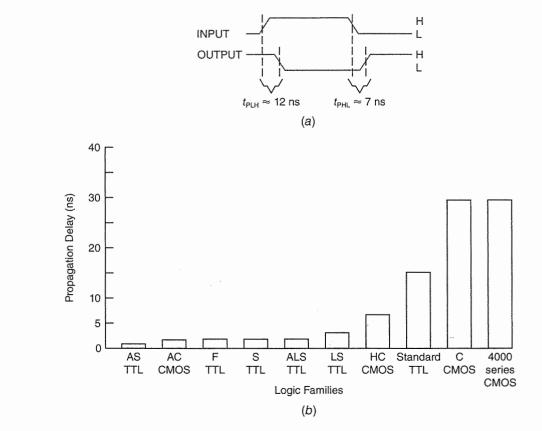

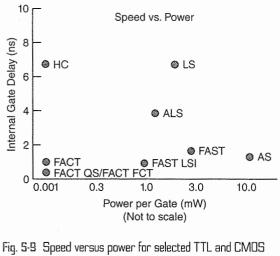

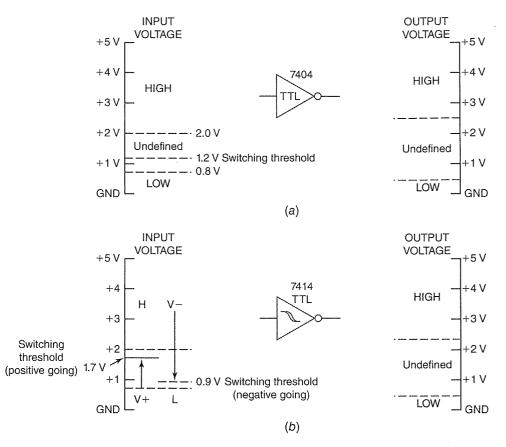

| The Exclusive NOR Gate 54            | 5-1 | Logic Levels and Noise Margin   | 141 |

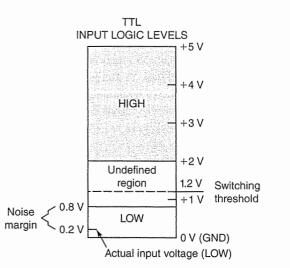

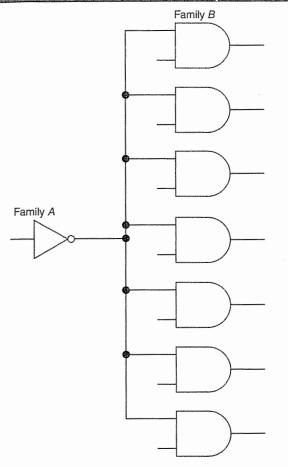

| The NAND Gate as a Universal Gate 56 | 5-2 | Other Digital IC Specifications | 146 |

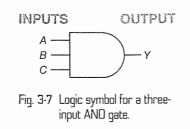

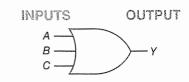

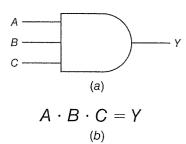

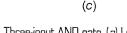

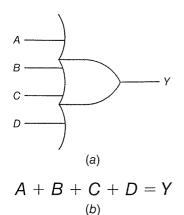

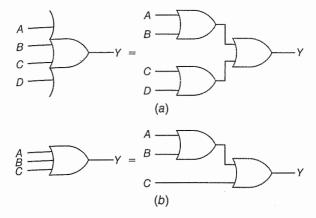

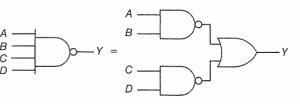

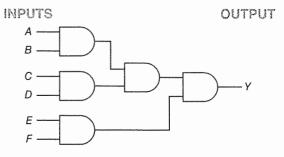

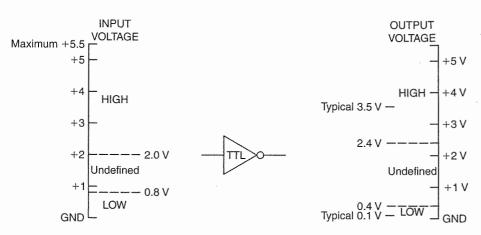

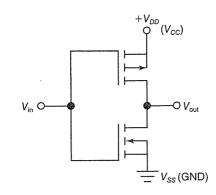

| Gates with More Than Two Inputs 57   | 5-3 | MOS and CMOS ICs                | 150 |

Contents

141

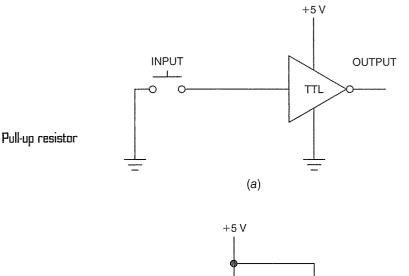

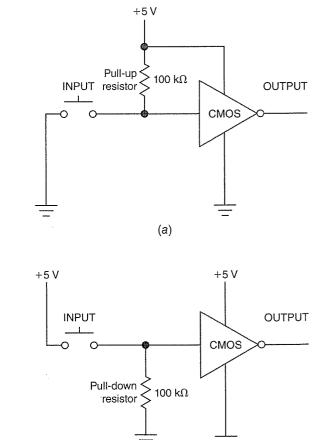

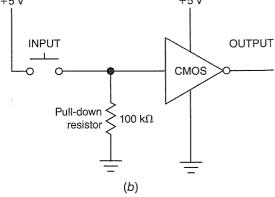

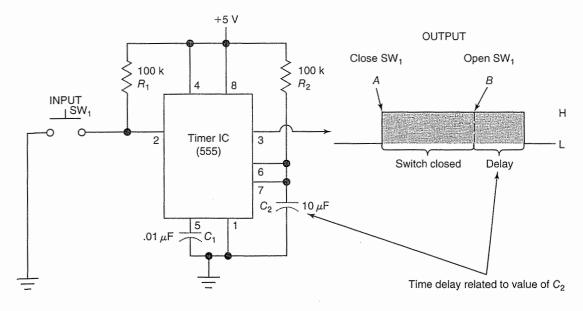

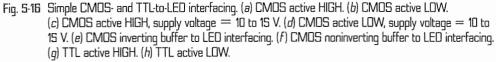

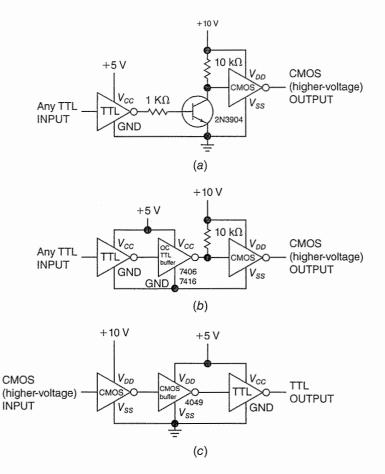

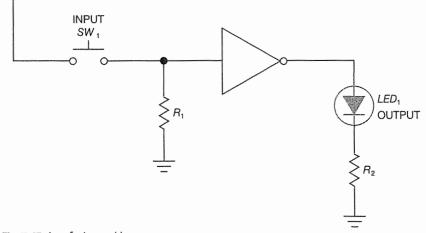

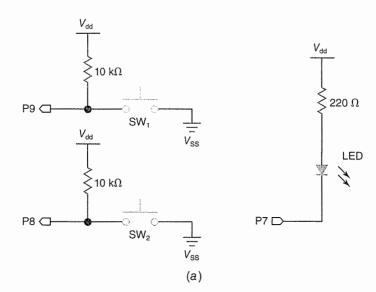

| 5-4                    | Interfacing TTL and CMOS with Switches    |       |

|------------------------|-------------------------------------------|-------|

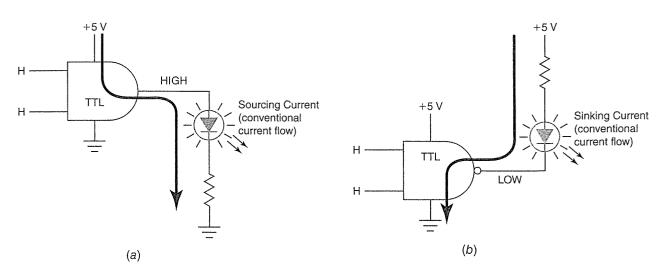

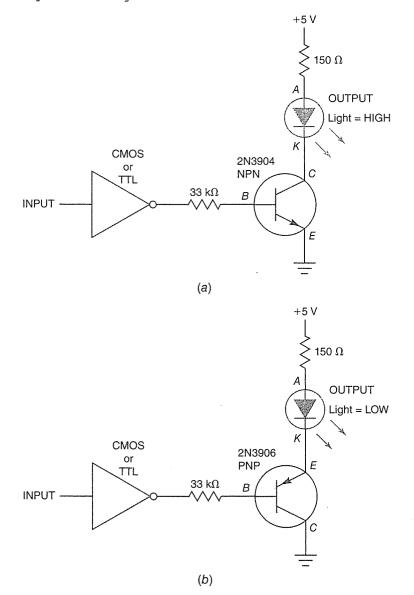

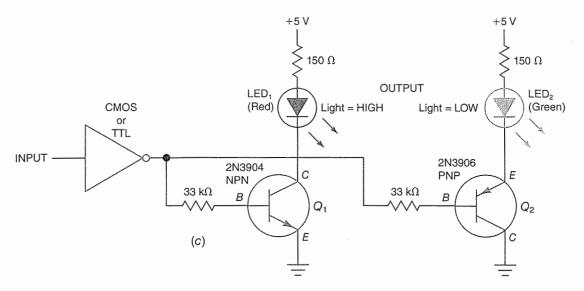

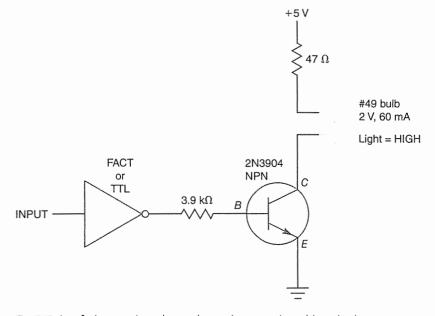

| 5-5                    | Interfacing TTL and CMOS with LEDs        |       |

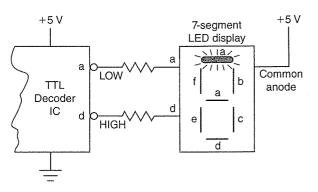

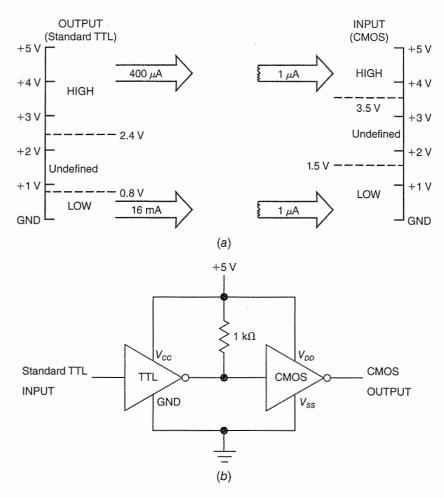

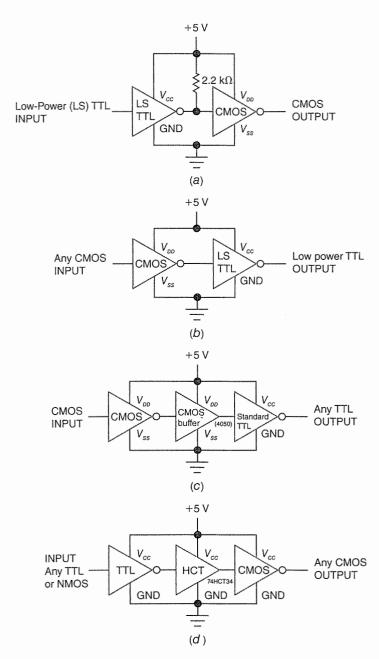

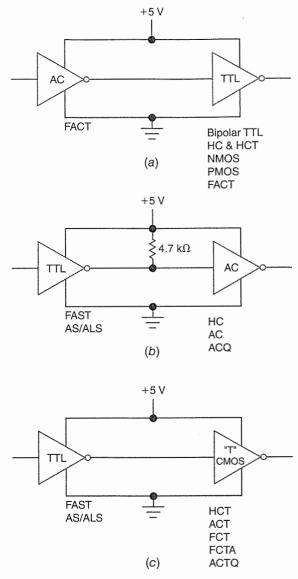

| 5-6                    | Interfacing TTL and CMOS ICs              | . 160 |

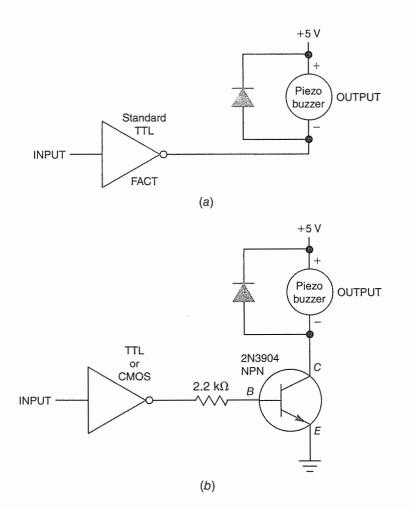

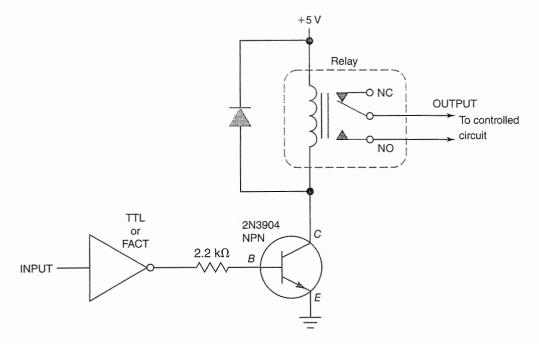

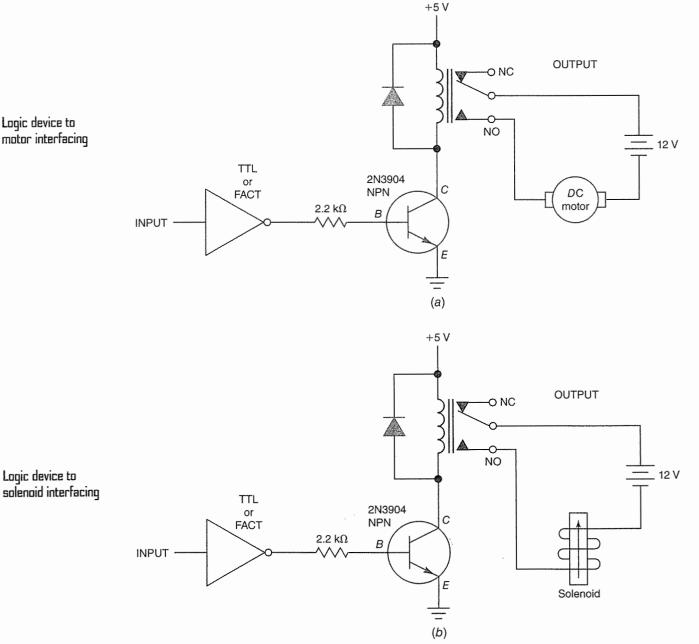

| 5-7                    | Interfacing with Buzzers, Relays,         |       |

|                        | Motors, and Solenoids                     |       |

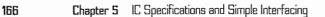

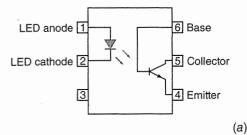

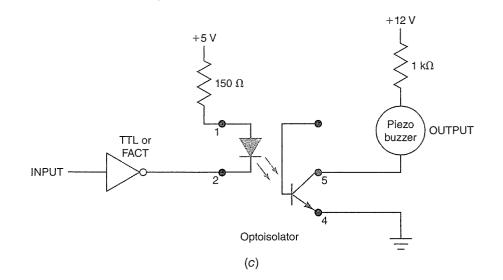

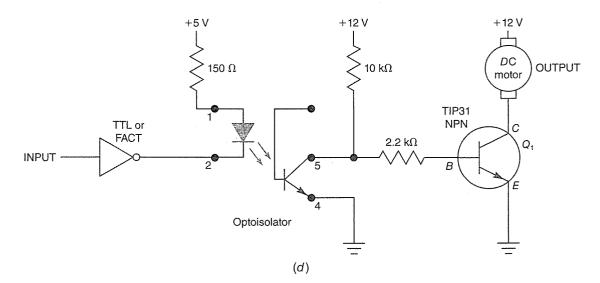

| 5-8                    | Optoisolators                             |       |

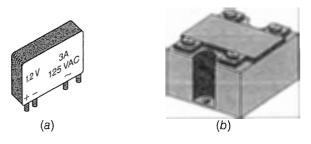

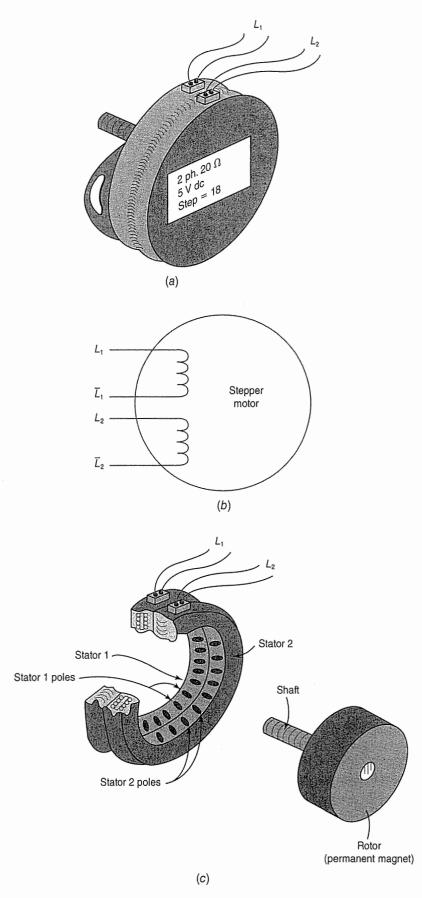

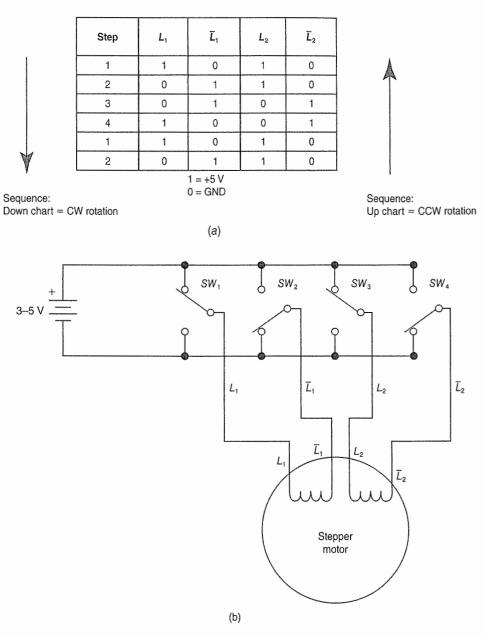

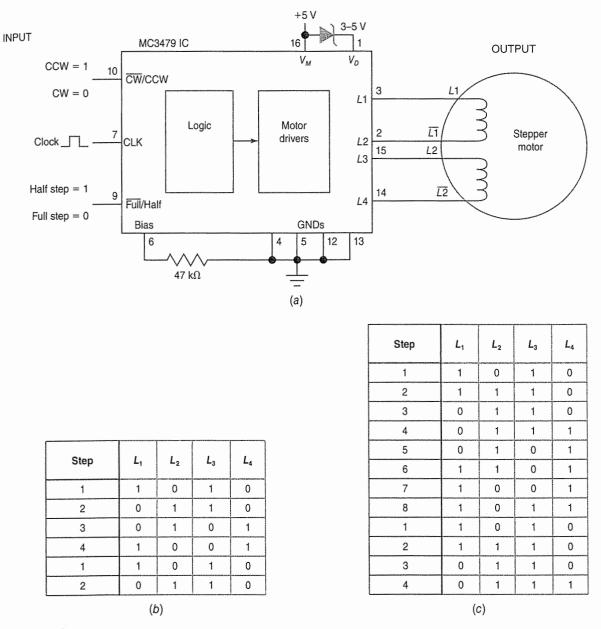

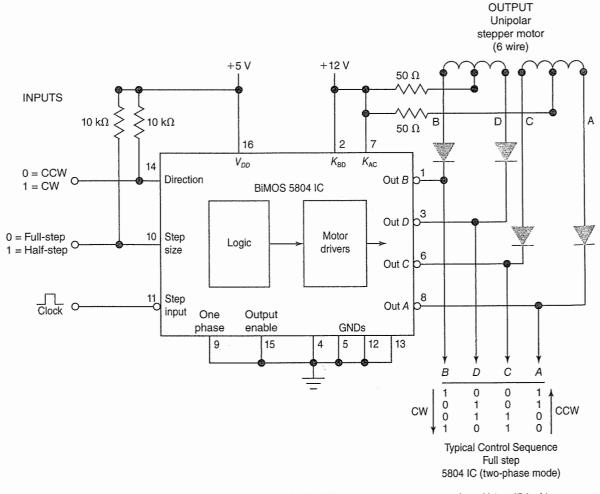

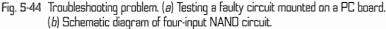

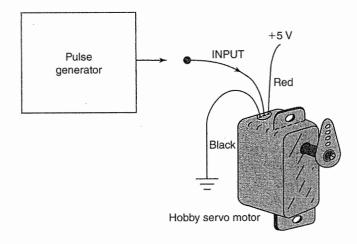

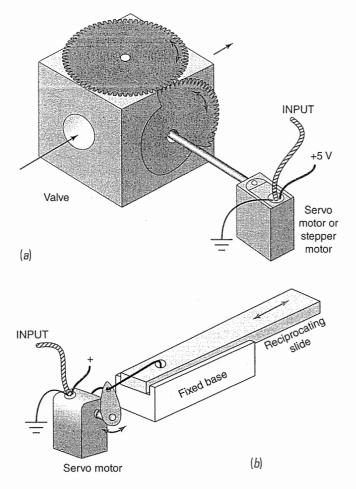

| 5-9                    | Interfacing with Servo and Stepper Motors | . 170 |

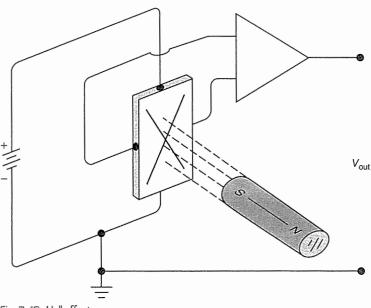

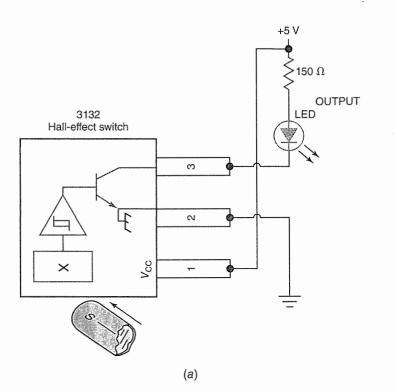

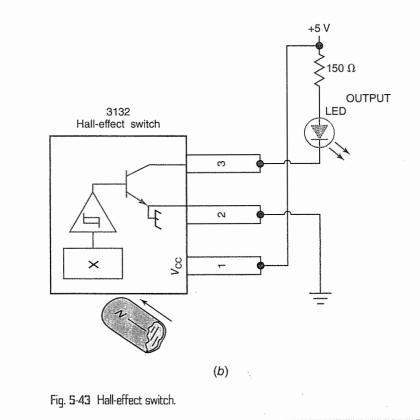

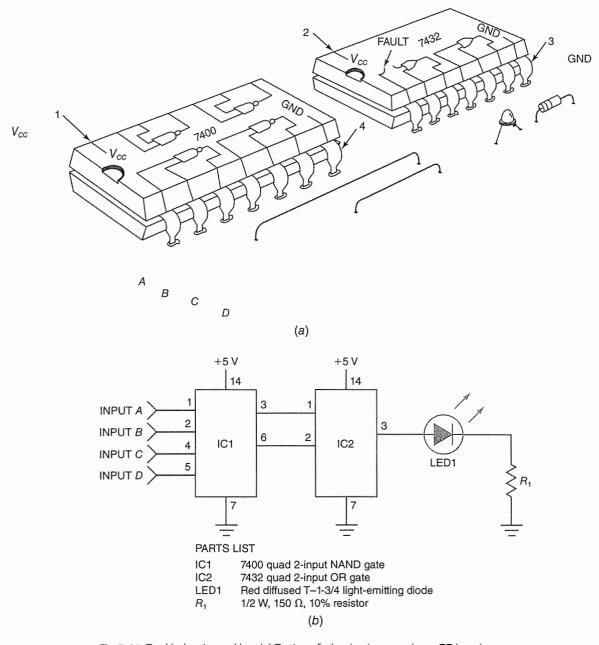

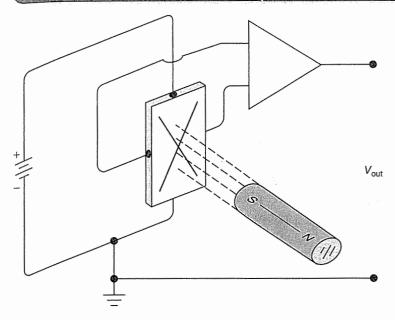

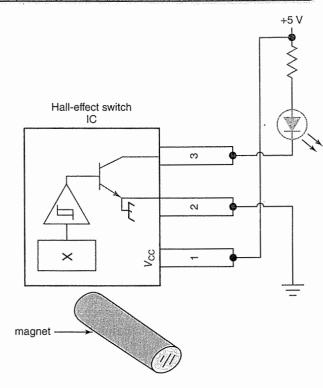

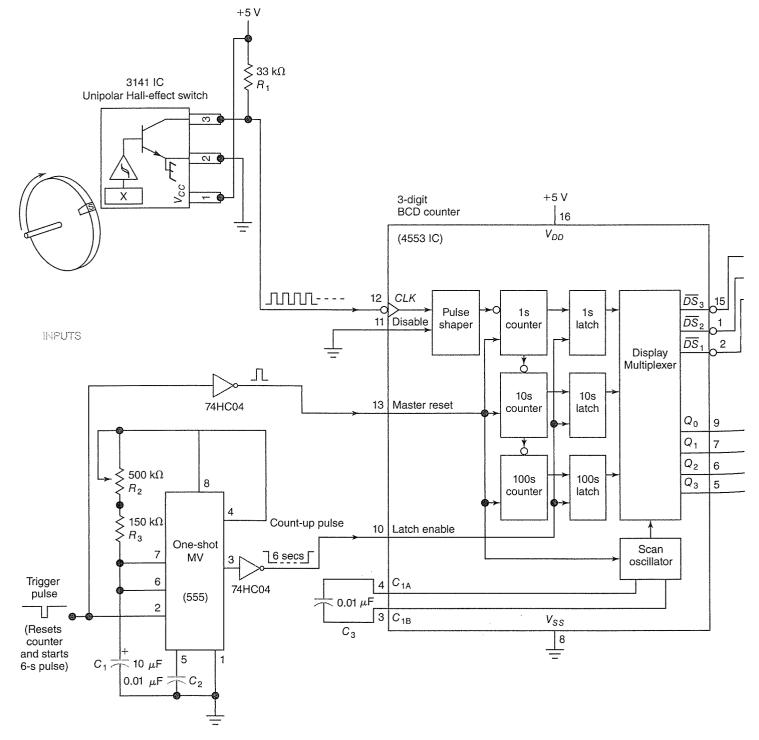

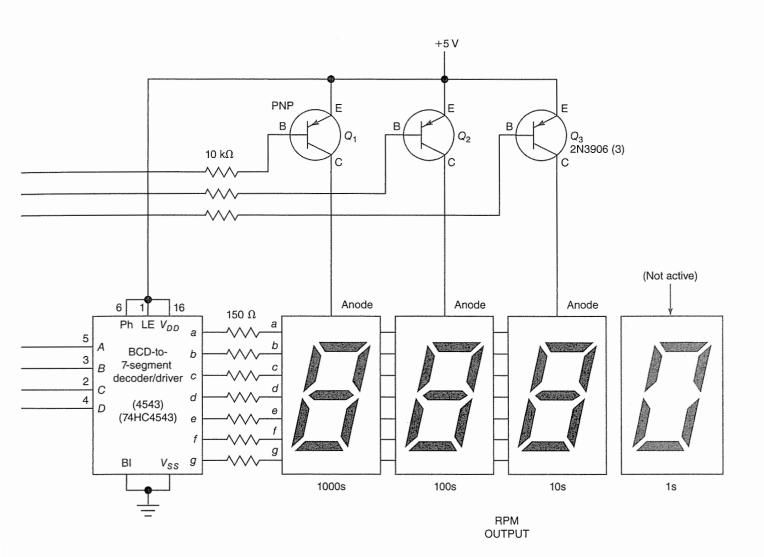

| 5-10                   | Using Hall-Effect Sensors.                | . 178 |

| 5-11                   | Troubleshooting Simple Logic Circuits     | . 185 |

| 5-12                   | Interfacing the Servo (BASIC Stamp        |       |

|                        | Module)                                   |       |

|                        | ary                                       |       |

| Chapte                 | r Review Questions                        | . 190 |

| Critical               | I Thinking Questions                      | . 194 |

| Answe                  | rs to Self-Tests                          | . 194 |

| Chapte                 | r 6 Encoding, Decoding, and               |       |

| Chupie                 | Seven-Segment Displays                    | 196   |

|                        |                                           |       |

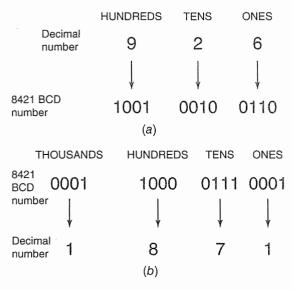

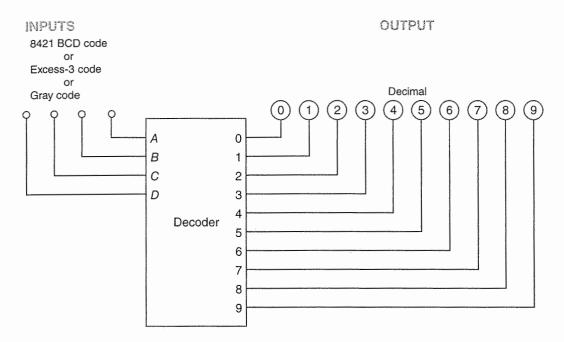

| 6-1                    | The 8421 BCD Code                         | . 196 |

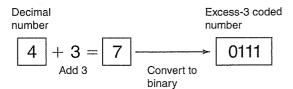

| 6-2                    | The Excess-3 Code                         | . 198 |

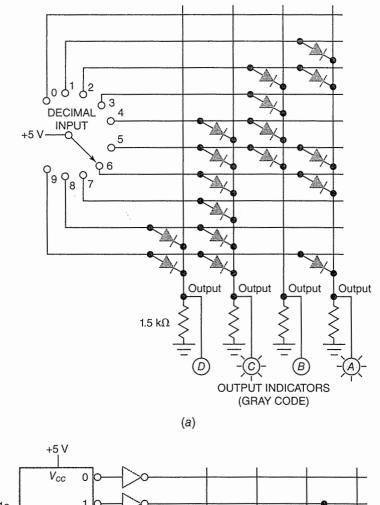

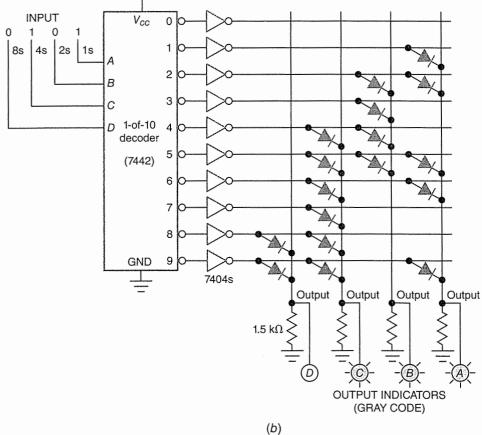

| 6-3                    | The Gray Code                             | . 199 |

| 6-4                    | The ASCII Code                            | . 202 |

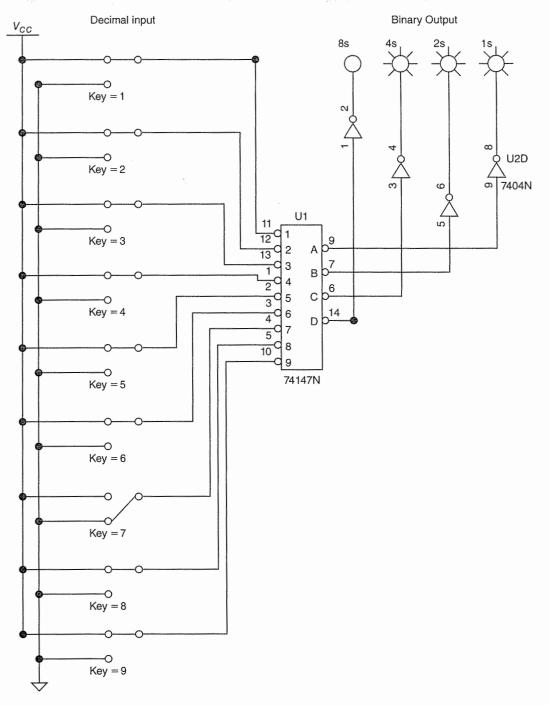

| 6-5                    | Encoders                                  | . 204 |

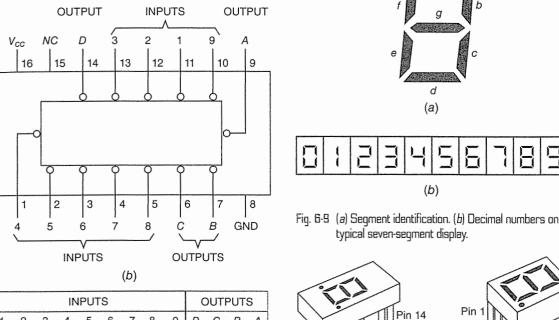

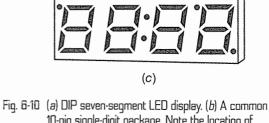

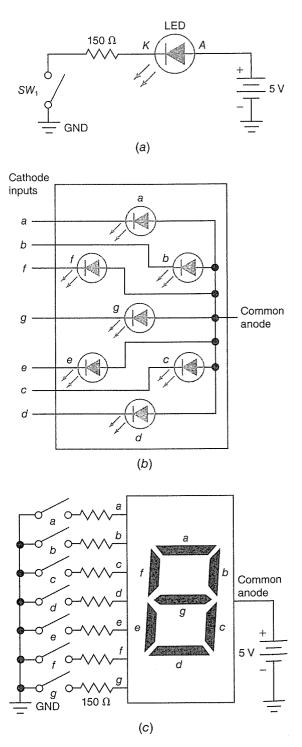

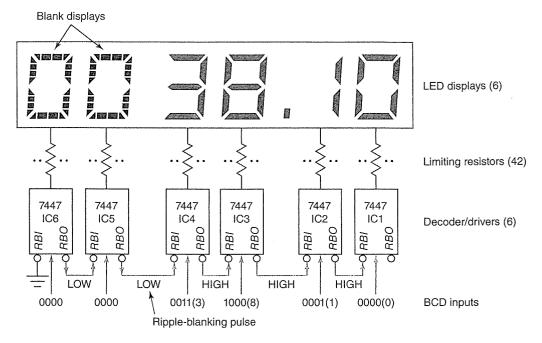

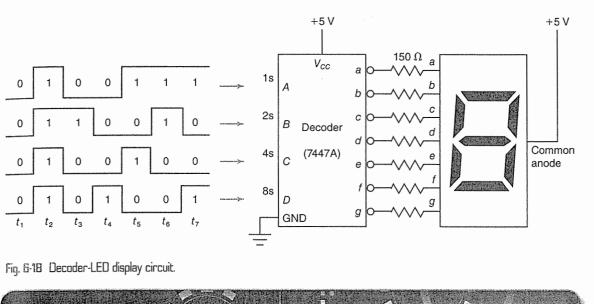

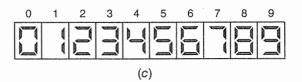

| 6-6                    | Seven-Segment LED Displays                | . 205 |

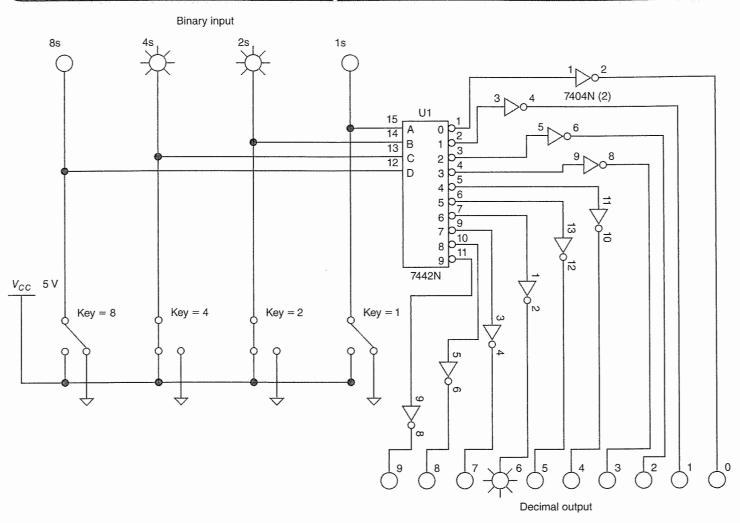

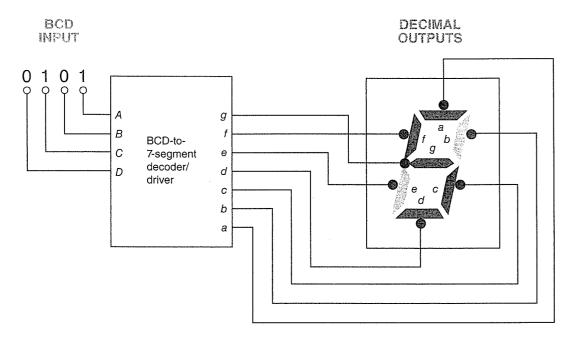

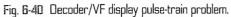

| 6-7                    | Decoders                                  | . 208 |

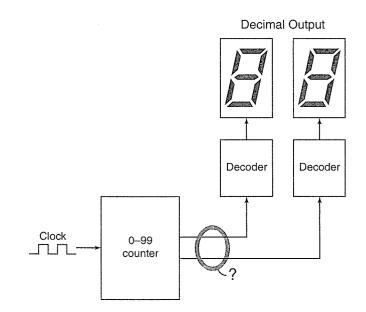

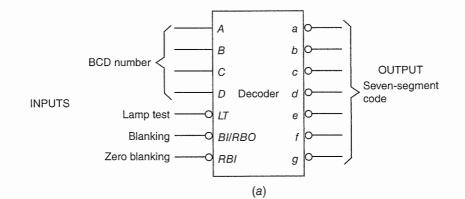

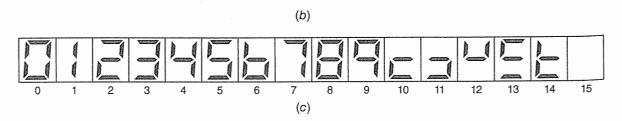

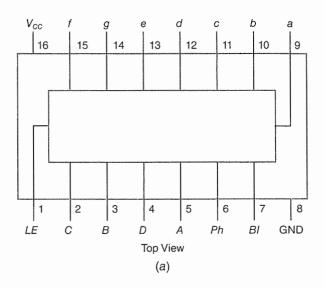

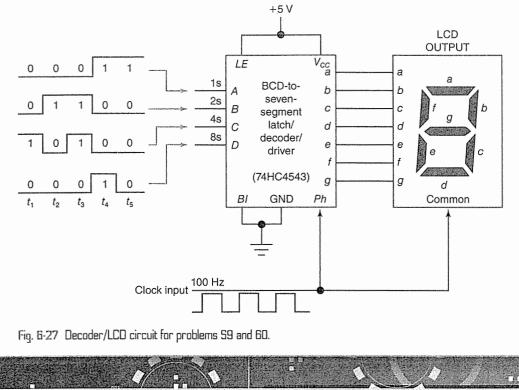

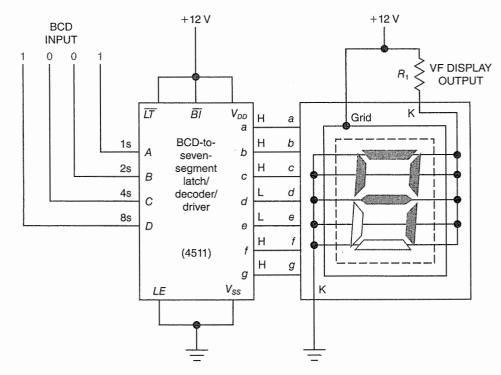

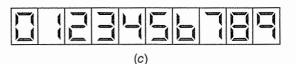

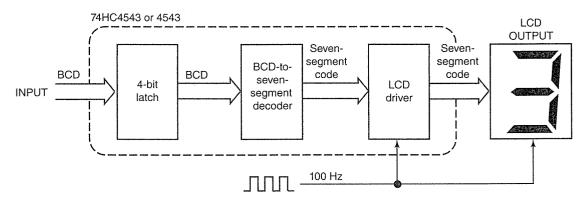

| 6-8                    | BCD-to-Seven-Segment Decoder/Drivers .    |       |

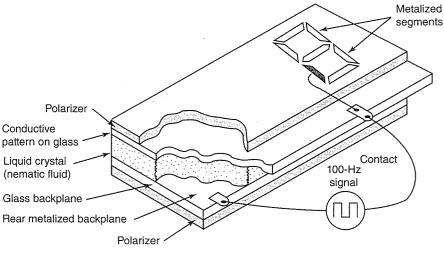

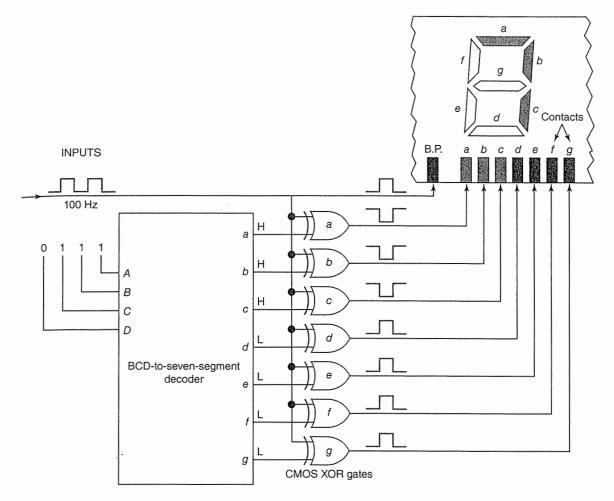

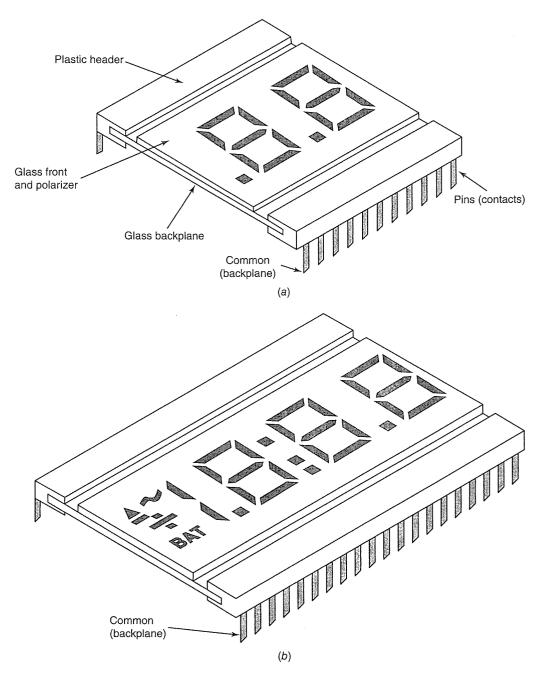

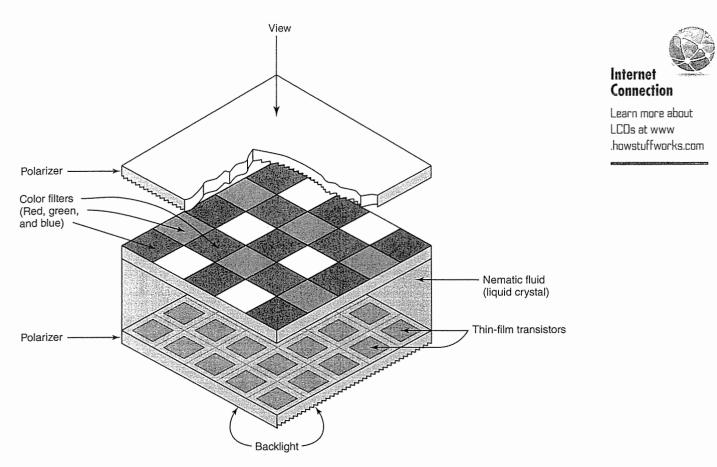

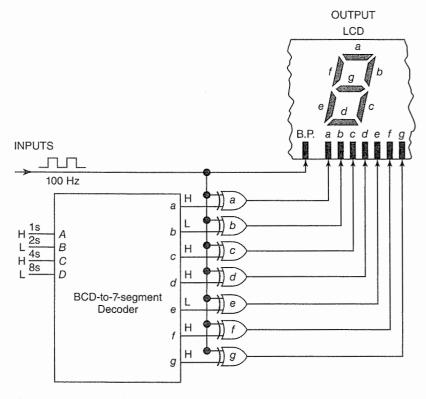

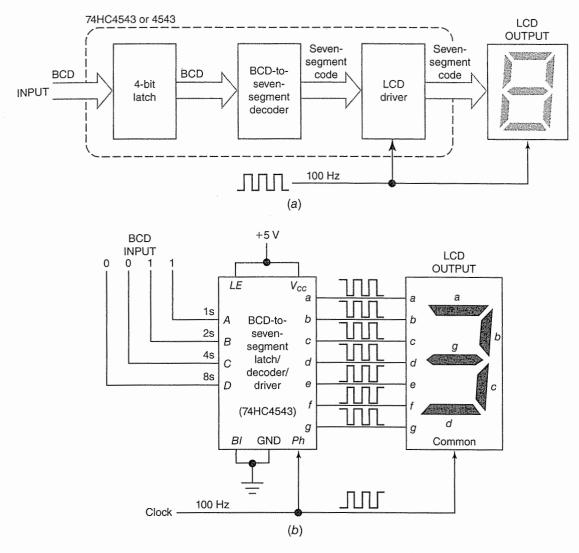

| 6-9                    | Liquid-Crystal Displays                   |       |

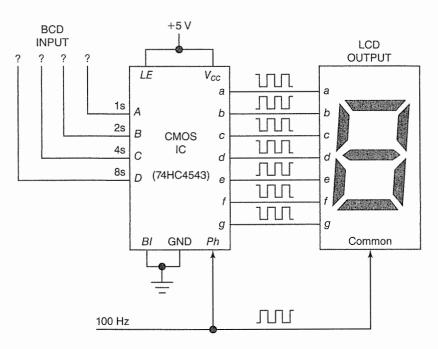

| 6-10                   | Using CMOS to Drive an LCD Display        |       |

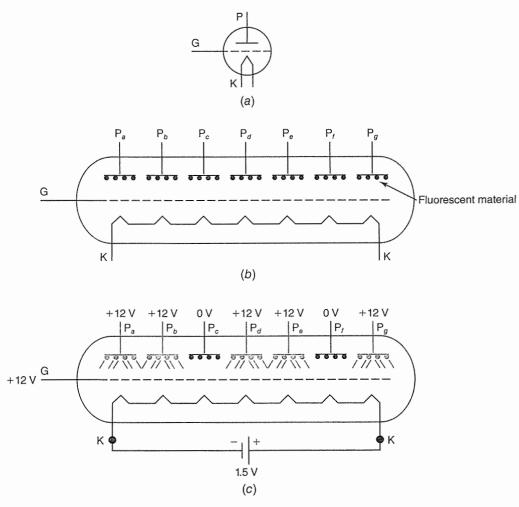

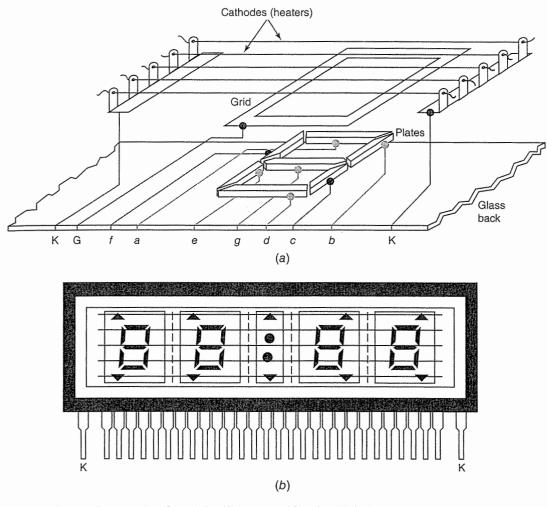

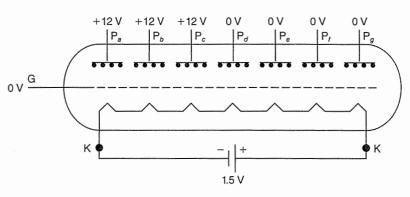

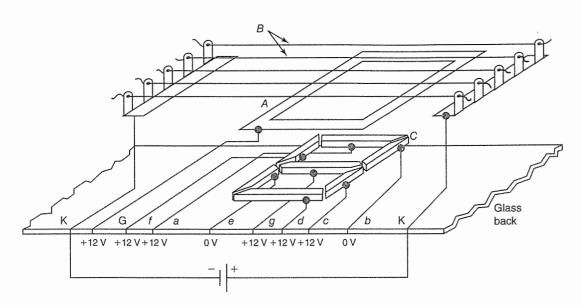

| 6-11                   | Vacuum Fluorescent Displays               |       |

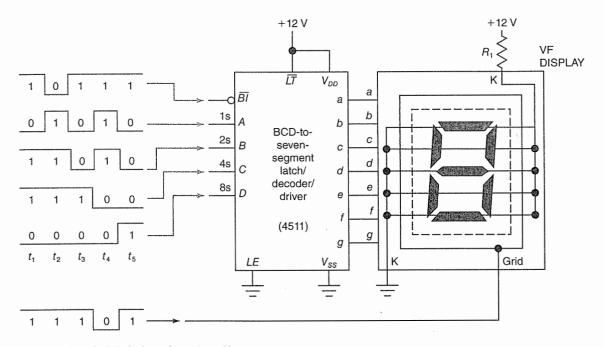

| 6-12                   | Driving a VF Display                      |       |

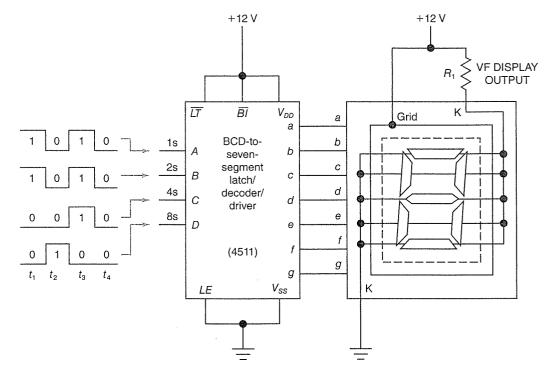

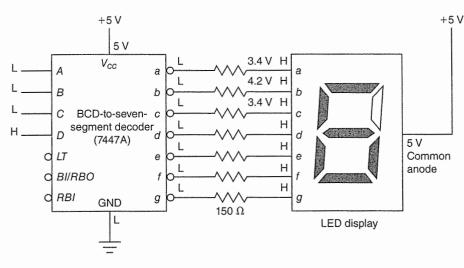

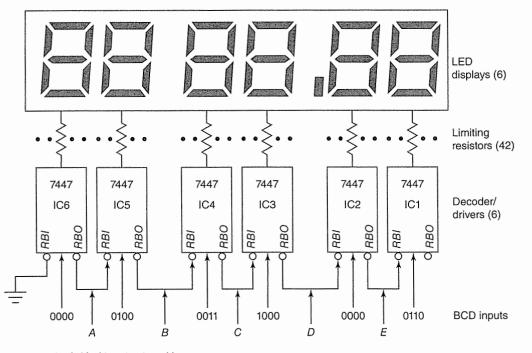

| 6-13                   | Troubleshooting a Decoding Circuit        |       |

|                        | ary                                       |       |

|                        | r Review Questions.                       |       |

|                        | 1 Thinking Questions                      |       |

|                        | rs to Self-Tests                          |       |

| 1 110 110              |                                           |       |

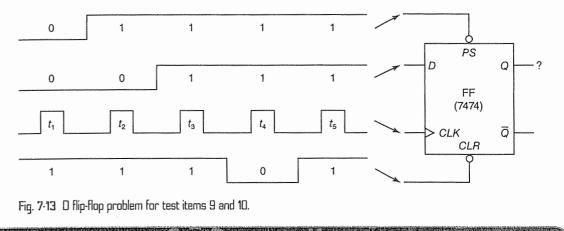

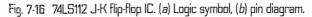

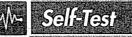

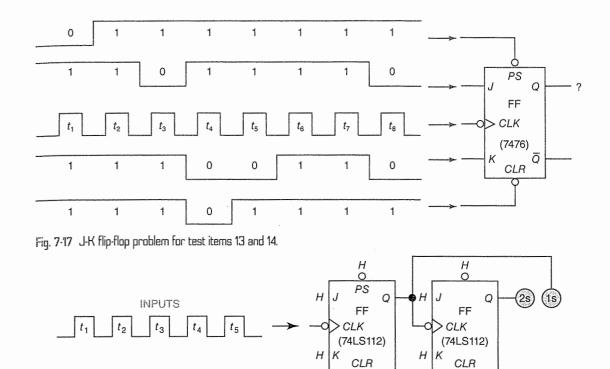

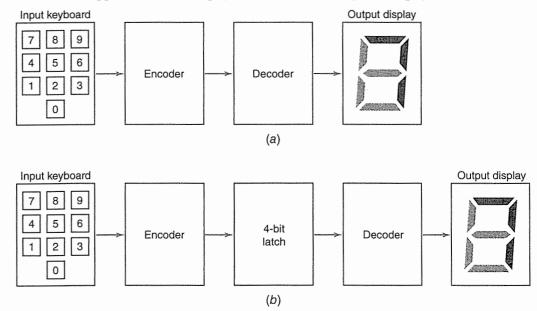

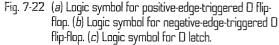

| Chapte                 | r 7 Flip-Flops                            | 236   |

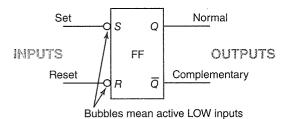

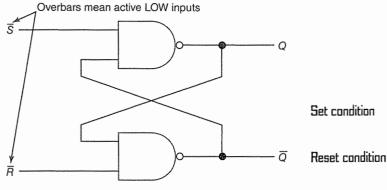

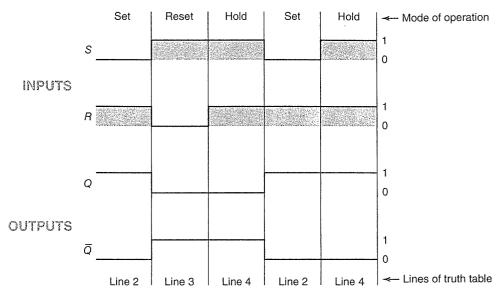

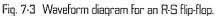

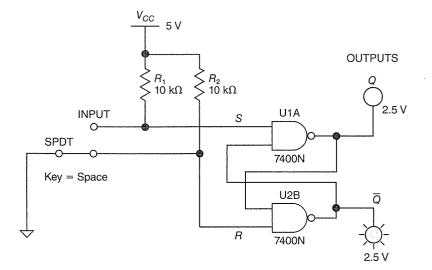

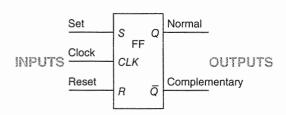

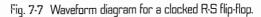

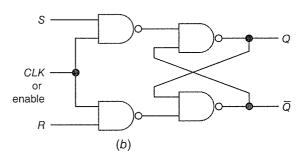

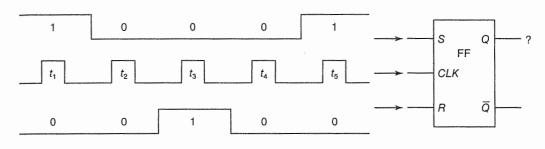

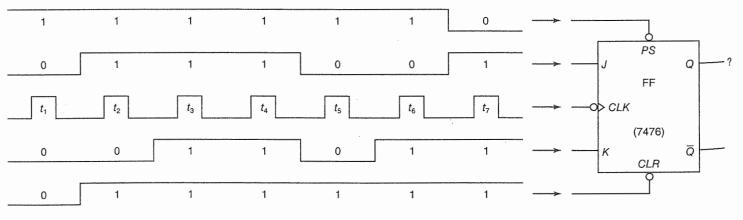

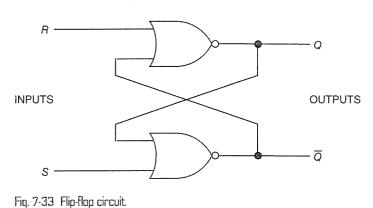

| 7-1                    | The R-S Flip-Flop                         | 236   |

| 7-2                    | The Clocked R-S Flip-Flop.                |       |

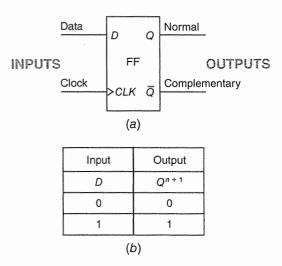

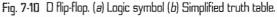

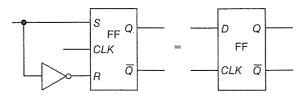

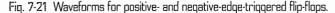

| 7-3                    | The D Flip-Flop                           |       |

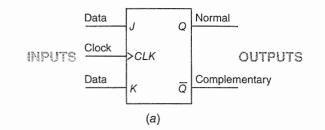

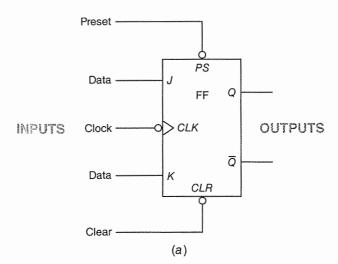

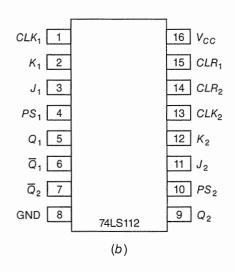

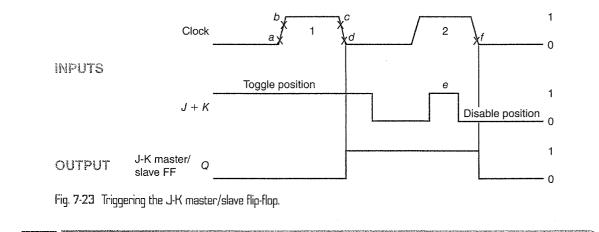

| 7-4                    | The J-K Flip-Flop                         |       |

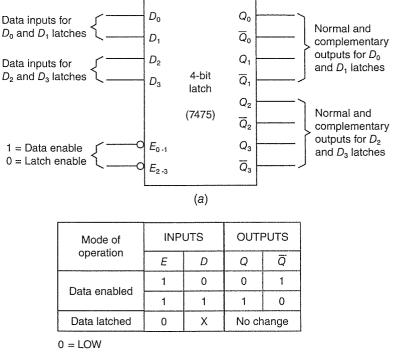

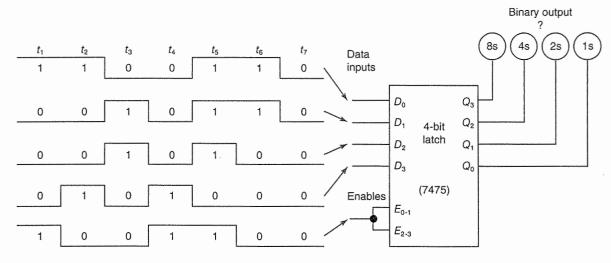

| 7- <del>4</del><br>7-5 | IC Latches                                |       |

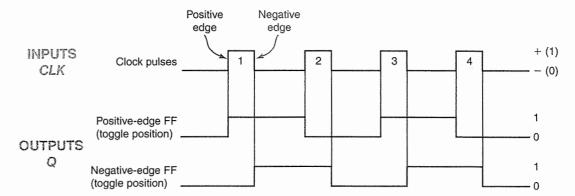

| 7-6                    | Triggering Flip-Flops                     |       |

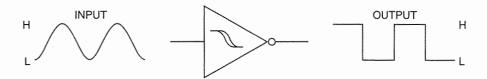

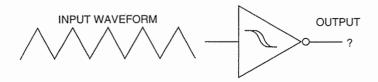

| 7-0<br>7-7             | Schmitt Trigger                           |       |

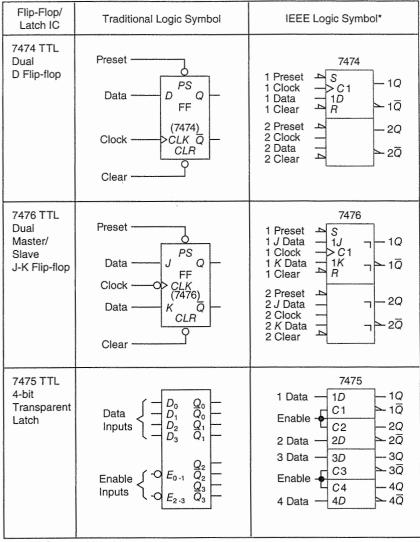

| 7-7<br>7-8             | IEEE Logic Symbols                        |       |

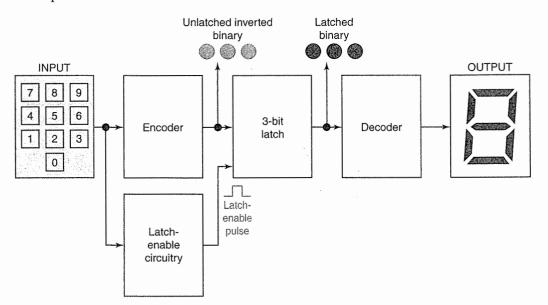

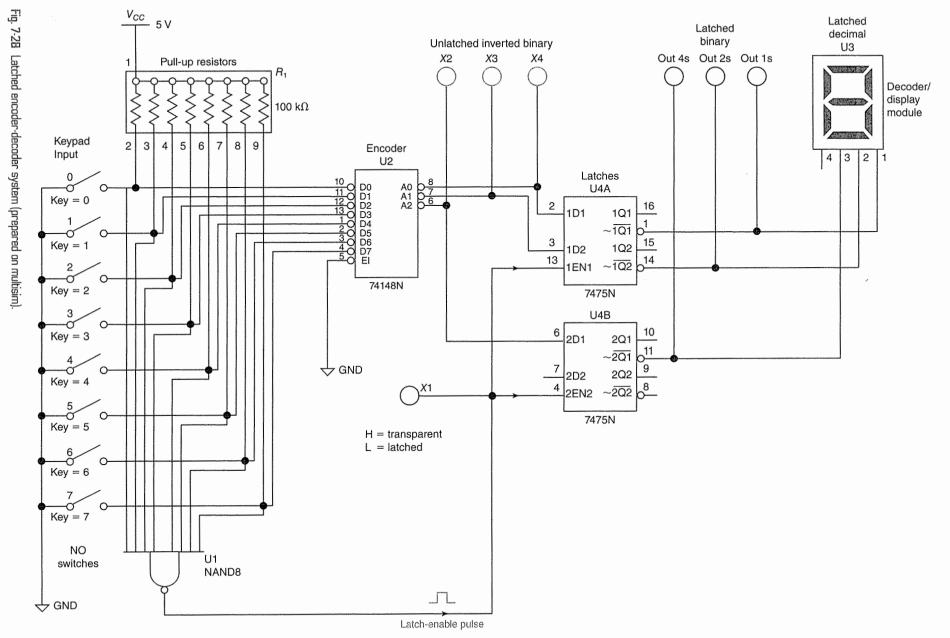

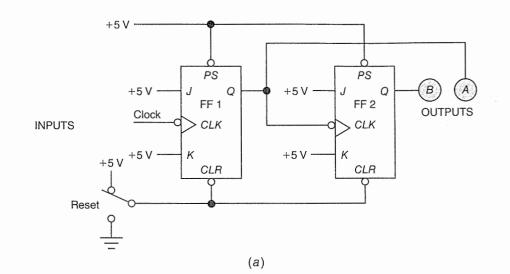

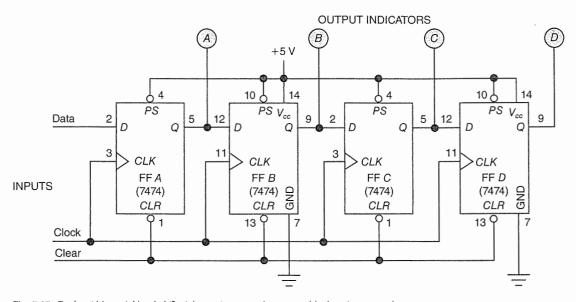

| 7-0<br>7-9             | Application: Latched Encoder-Decoder      | . 232 |

| 1-7                    | System.                                   | . 254 |

| Summe                  | ary                                       |       |

|                        | r Review Questions                        |       |

|                        | 1 Thinking Questions                      |       |

|                        | rs to Self-Tests                          |       |

| 7113 WC                |                                           | . 200 |

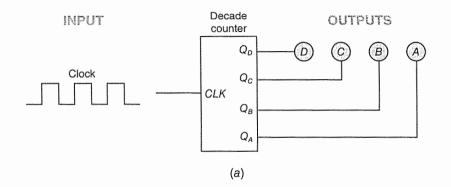

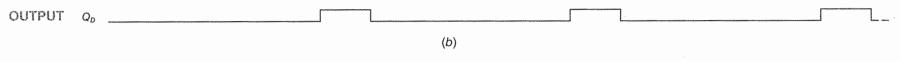

| Chapte | er 8 Counters                         | 262 |

|--------|---------------------------------------|-----|

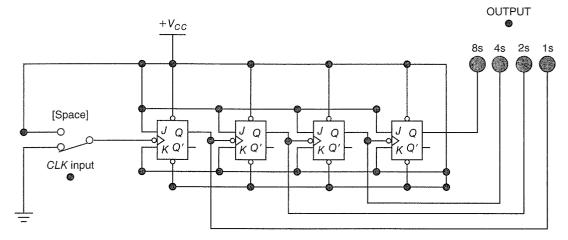

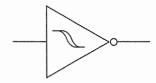

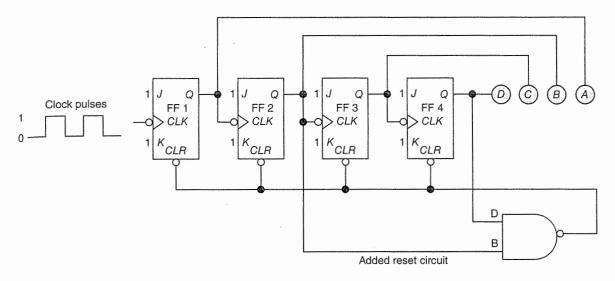

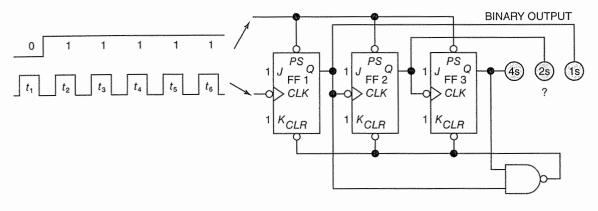

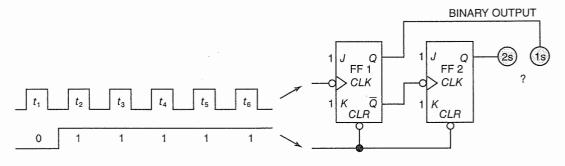

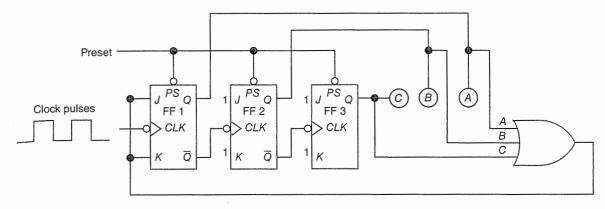

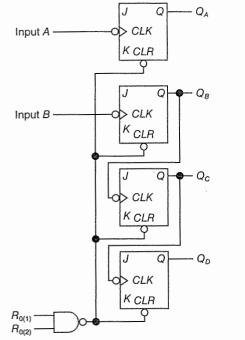

| 8-1    | Ripple Counters                       | 262 |

| 8-2    | Mod-10 Ripple Counters                |     |

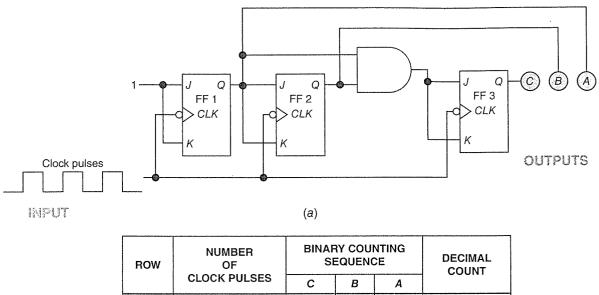

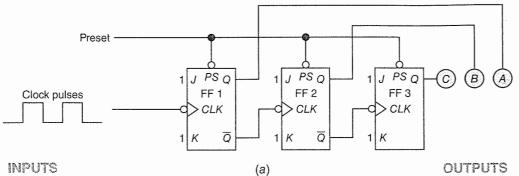

| 8-3    | Synchronous Counters                  |     |

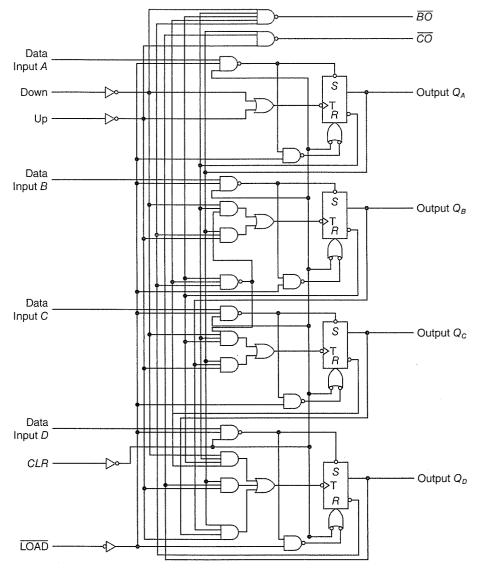

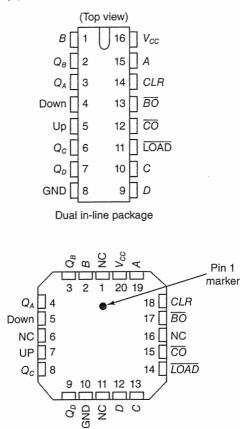

| 8-4    | Down Counters                         |     |

| 8-5    | Self-Stopping Counters                | 269 |

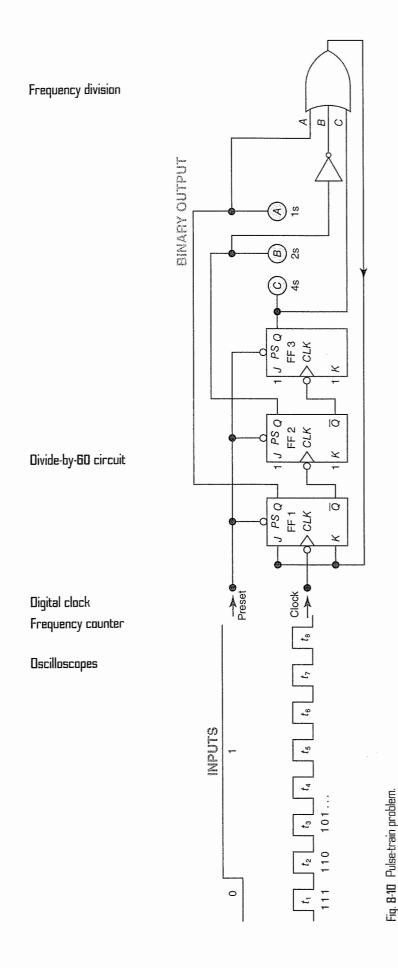

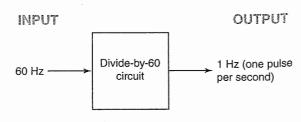

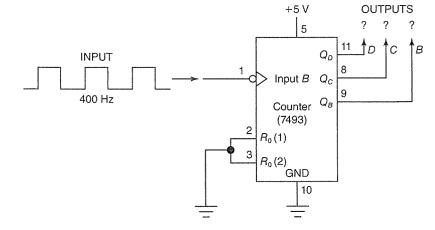

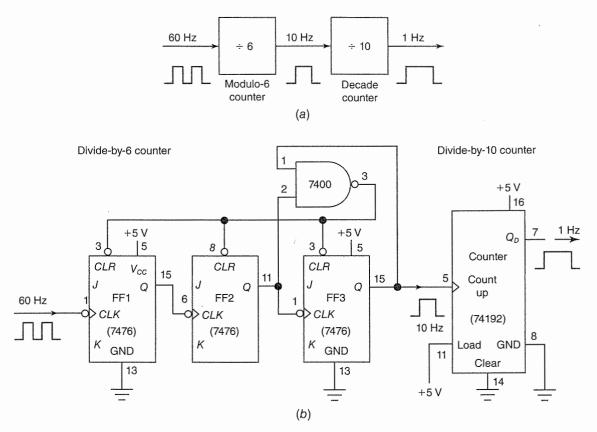

| 8-6    | Counters as Frequency Dividers        | 270 |

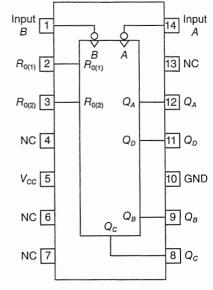

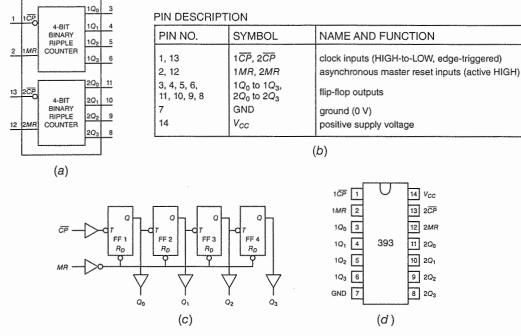

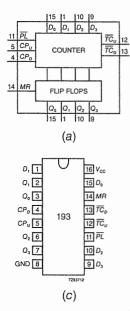

| 8-7    | TTL IC Counters.                      |     |

| 8-8    | CMOS IC Counters.                     | 276 |

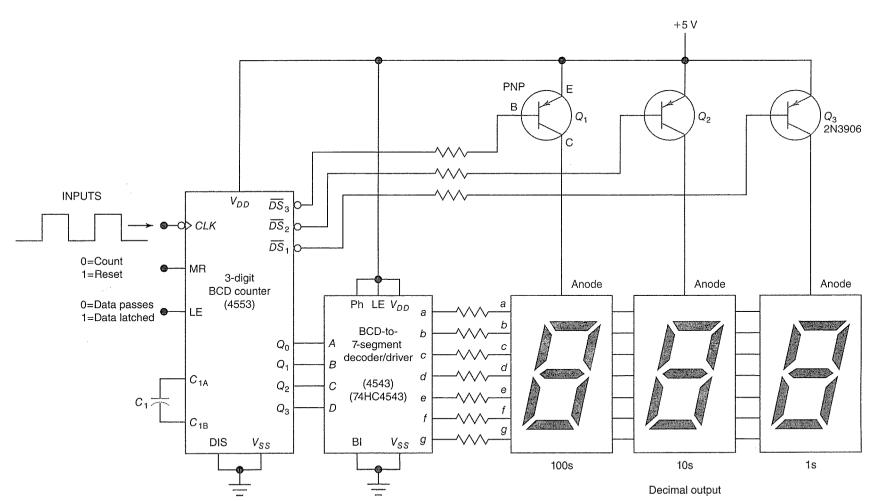

| 8-9    | A Three-Digit BCD Counter             | 280 |

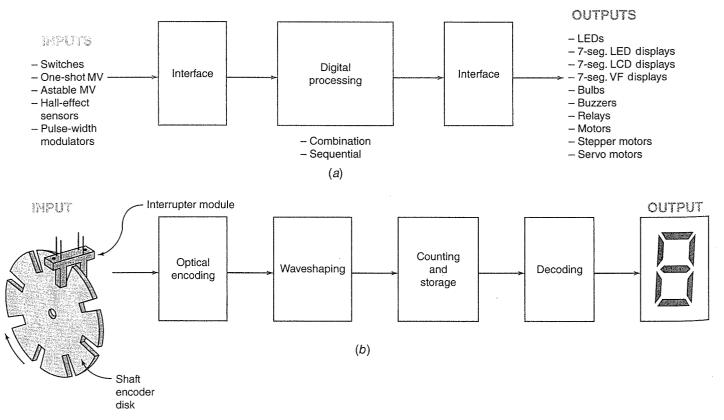

| 8-10   | Counting Real-World Events            | 284 |

| 8-11   | Using a CMOS Counter in an Electronic |     |

|        | Game                                  | 288 |

| 8-12   | Using Counters—An Experimental        |     |

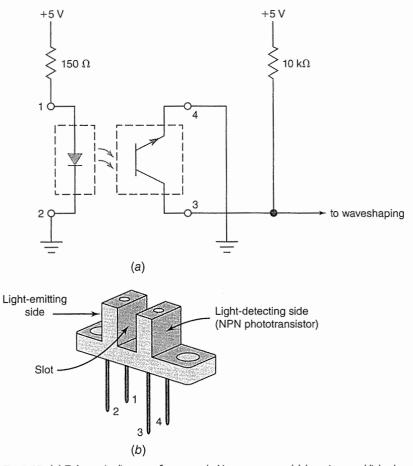

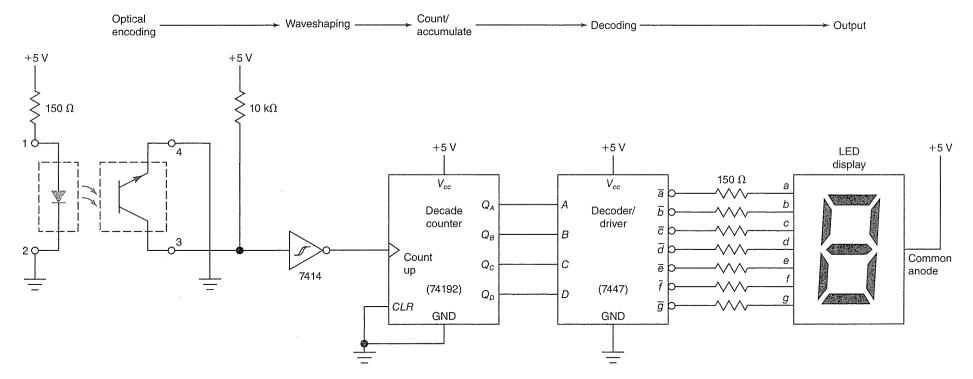

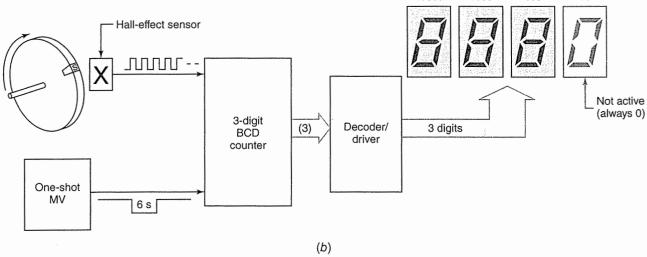

|        | Tachometer                            | 291 |

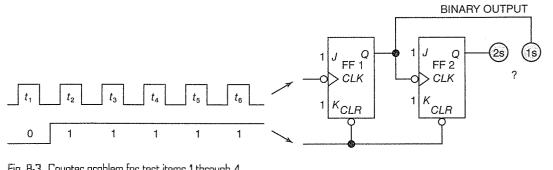

| 8-13   | Troubleshooting a Counter             |     |

| Summ   | ary                                   |     |

|        | er Review Questions                   |     |

|        | ll Thinking Questions                 |     |

|        | ers to Self-Tests                     |     |

|        |                                       |     |

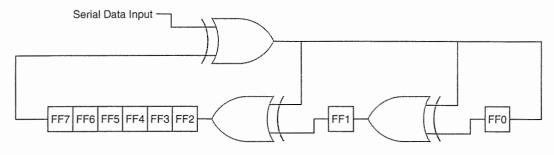

| Chapter | r 9 Shift Registers                     | 305 |

|---------|-----------------------------------------|-----|

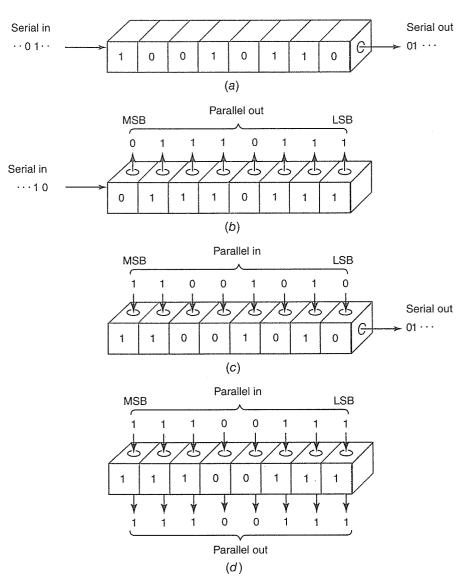

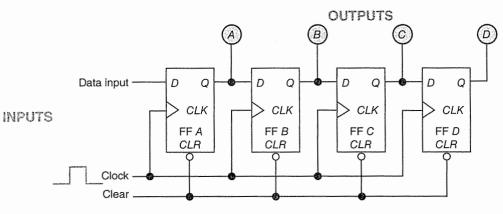

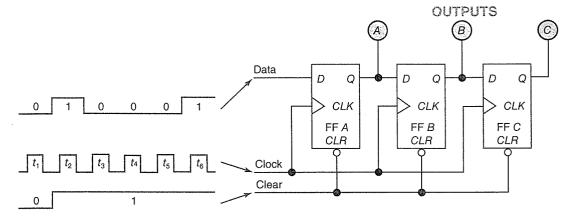

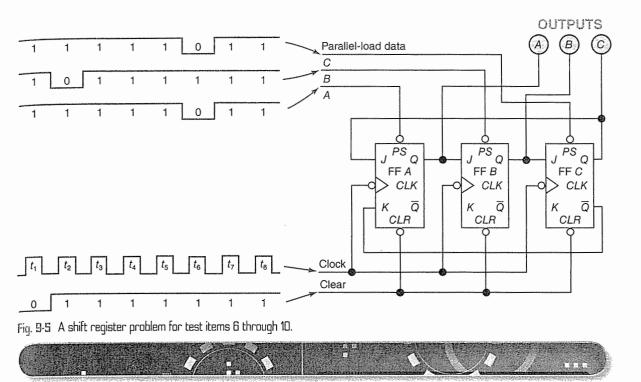

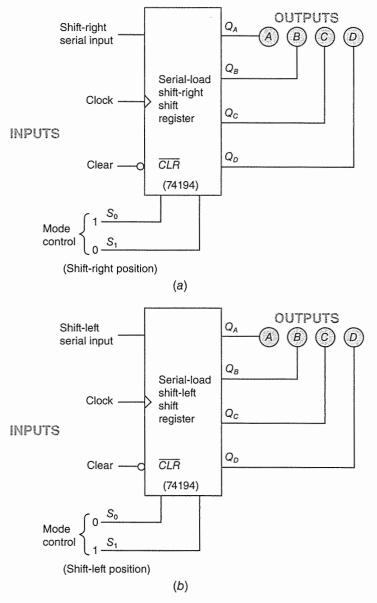

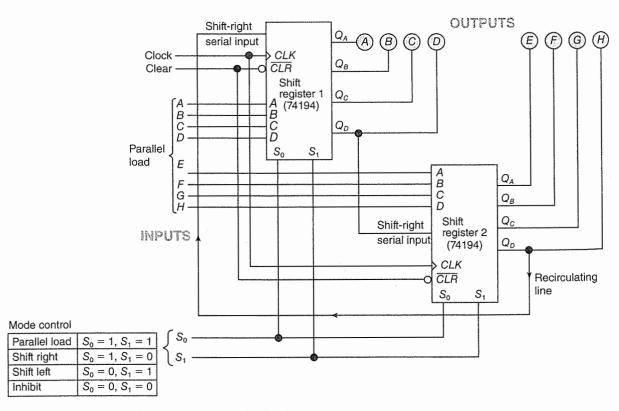

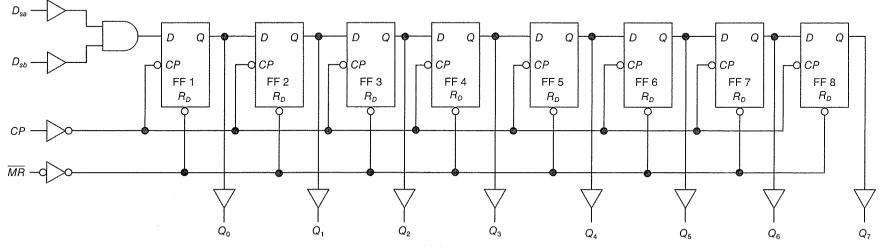

| 9-1     | Serial-Load Shift Registers             | 307 |

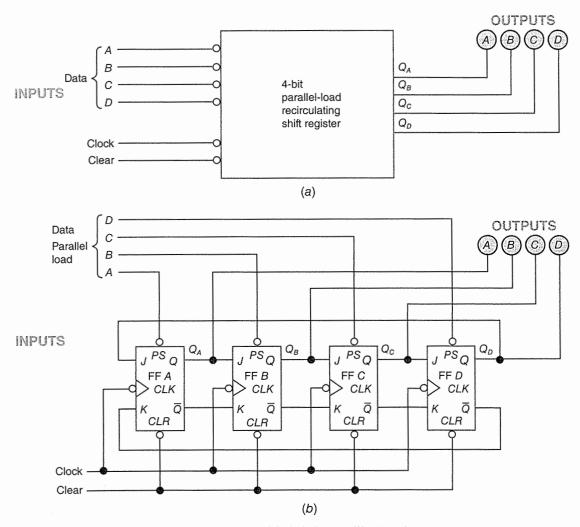

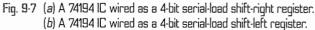

| 9-2     | Parallel-Load Shift Registers           | 308 |

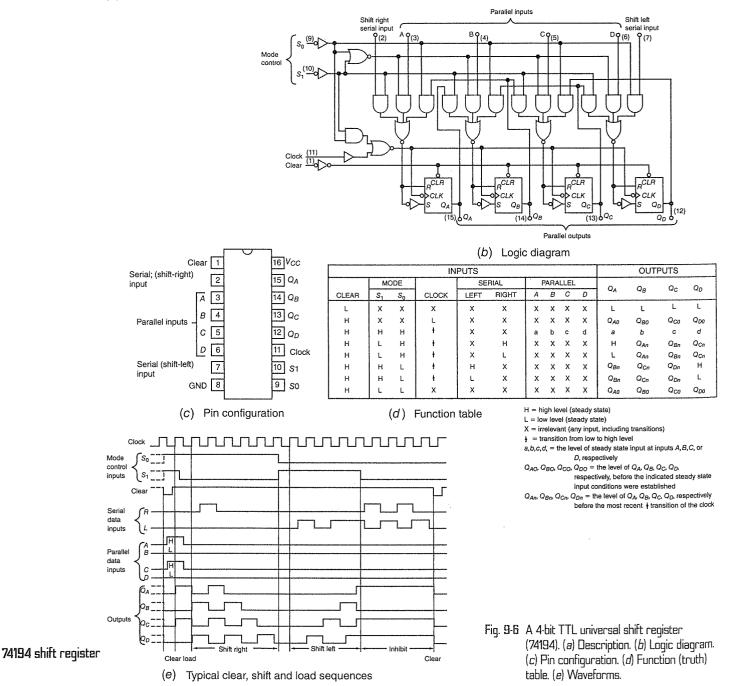

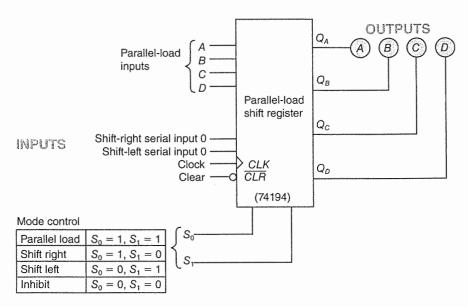

| 9-3     | A Universal Shift Register              | 311 |

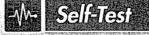

| 9-4     | Using the 74194 IC Shift Register       | 313 |

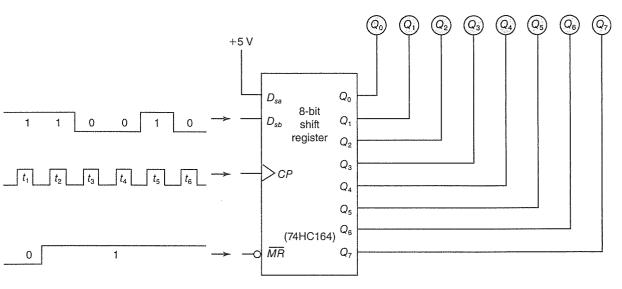

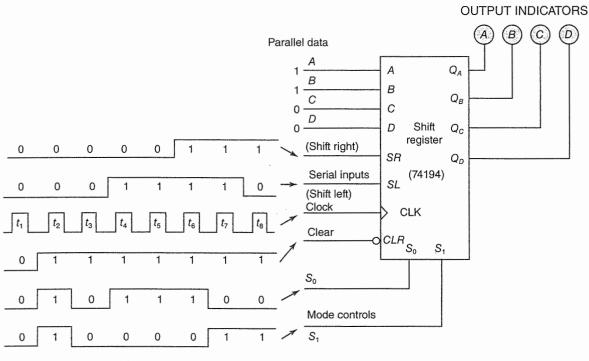

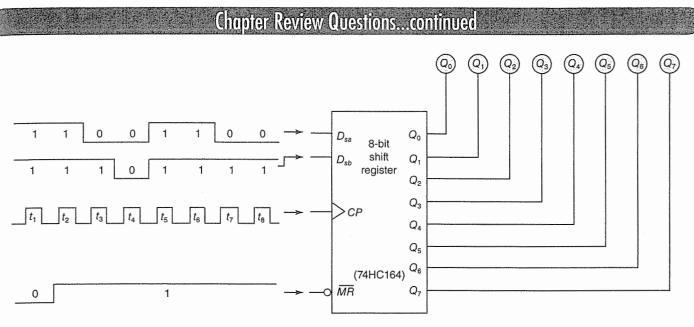

| 9-5     | An 8-Bit CMOS Shift Register            | 315 |

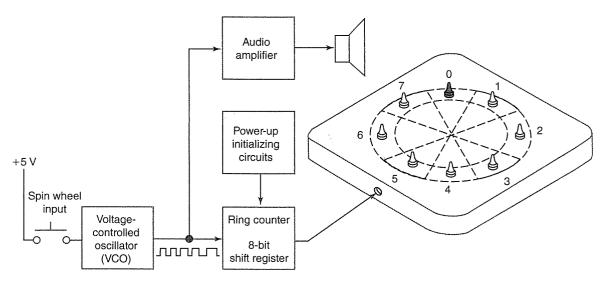

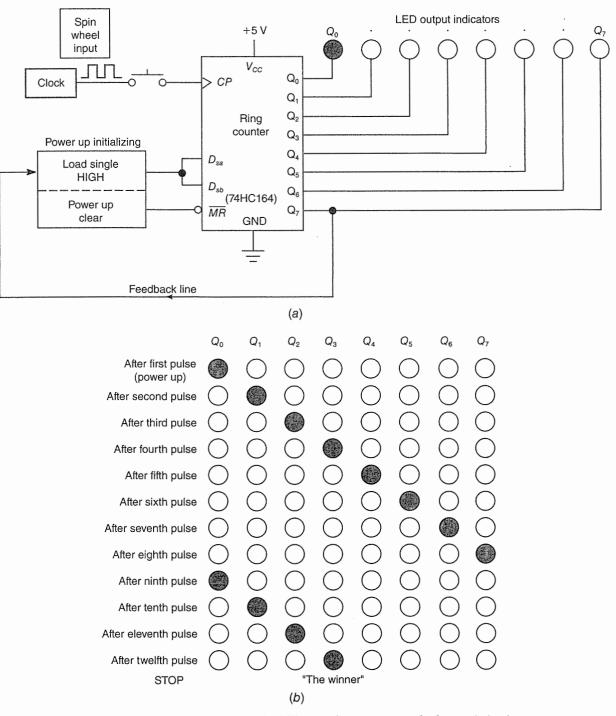

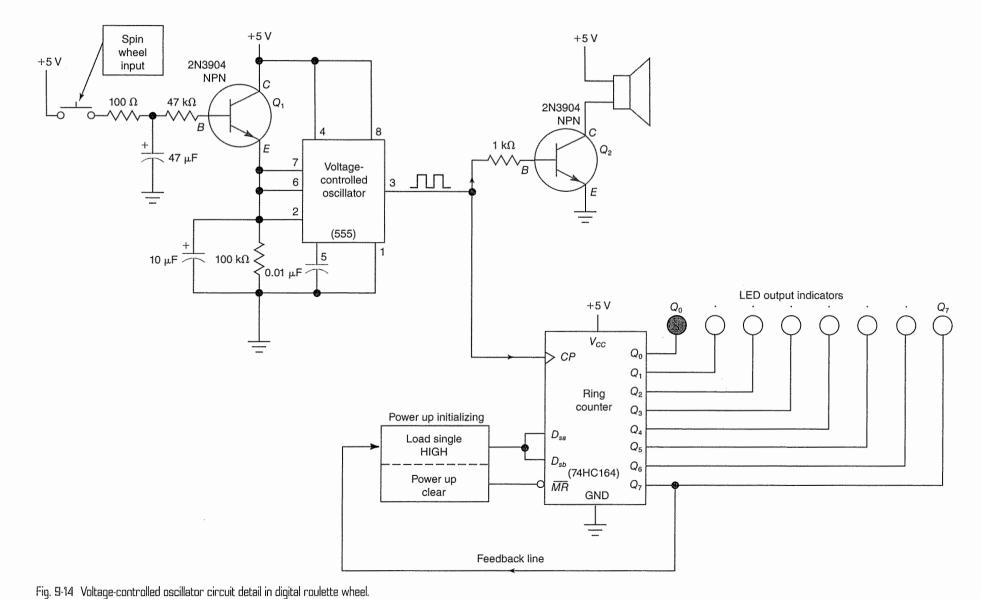

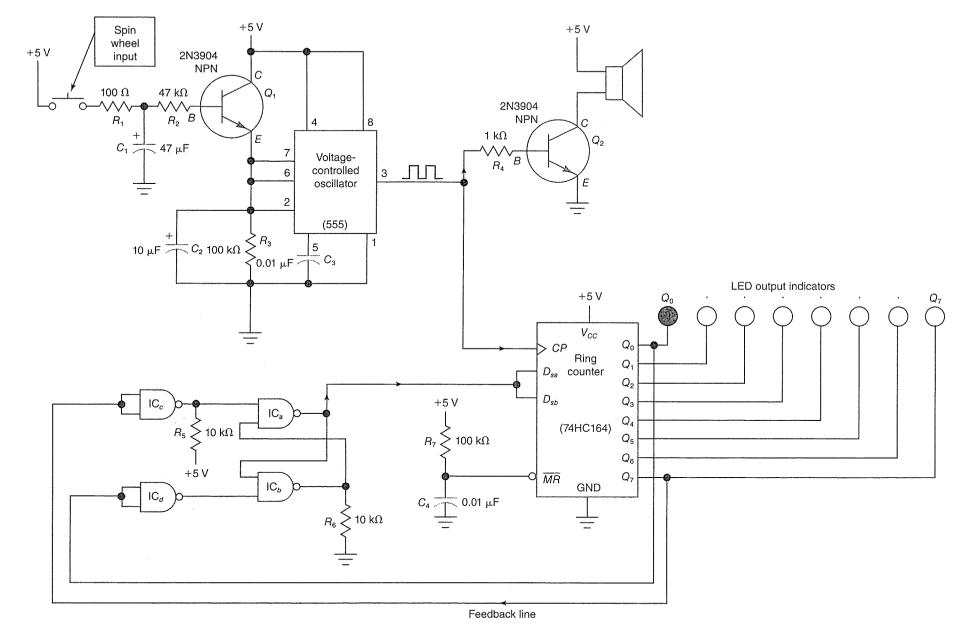

| 9-6     | Using Shift Registers: Digital Roulette | 318 |

| 9-7     | Troubleshooting a Simple Shift Register | 323 |

| Summa   | ury                                     | 325 |

| Chapte  | Review Questions                        | 325 |

| -       | Thinking Questions                      |     |

|         | rs to Self-Tests                        |     |

330

| Chapter 10 | Arithmetic | Circuits |

|------------|------------|----------|

|------------|------------|----------|

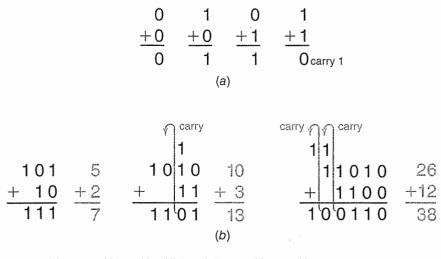

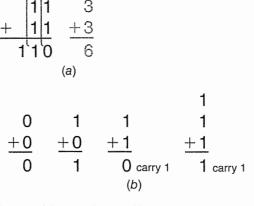

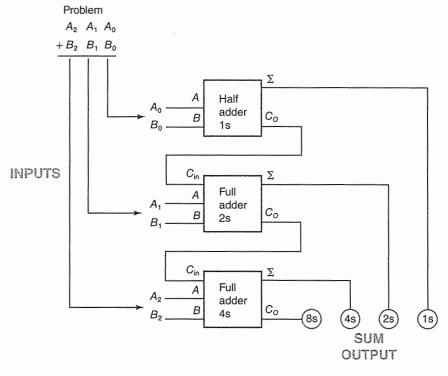

| 10-1    | Binary Addition                      |

|---------|--------------------------------------|

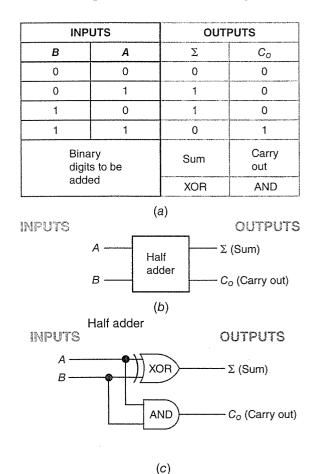

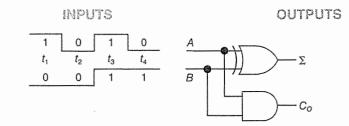

| 10-2    | Half Adders                          |

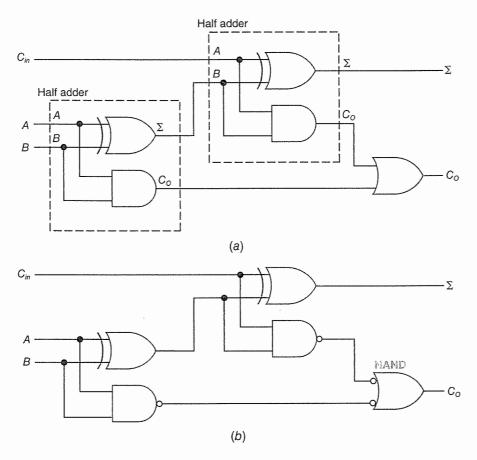

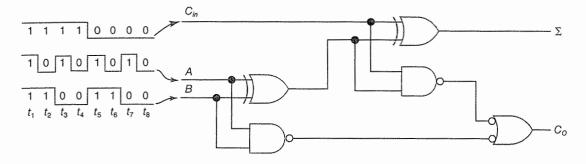

| 10-3    | Full Adders                          |

| 10-4    | 3-Bit Adders                         |

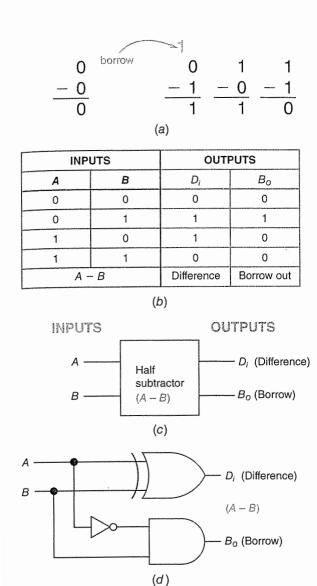

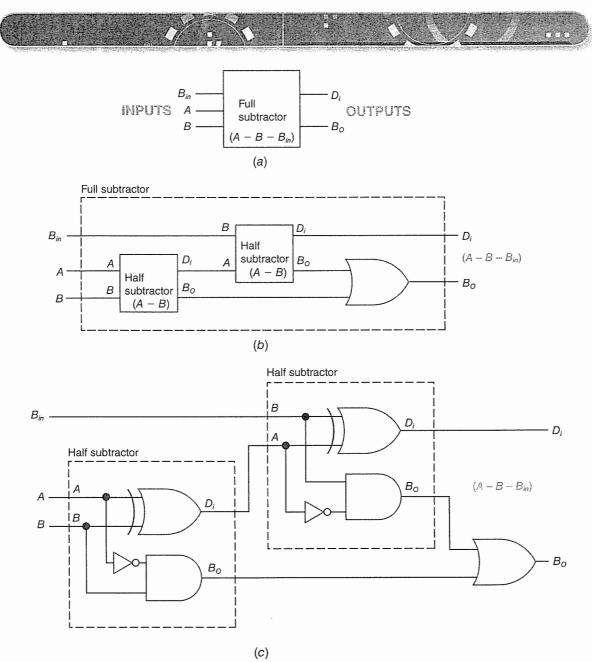

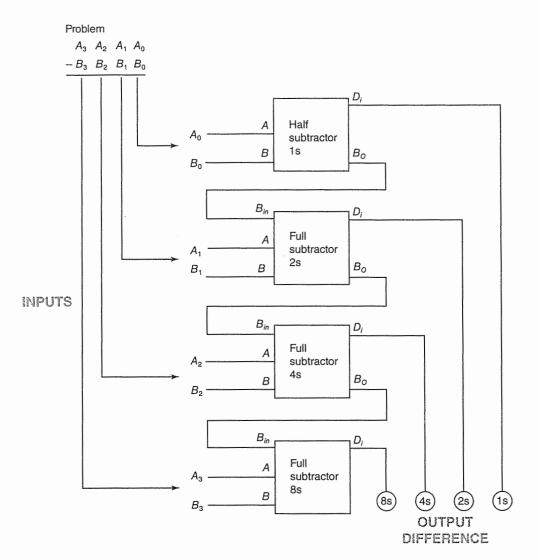

| 10-5    | Binary Subtraction                   |

| 10-6    | Parallel Subtractors                 |

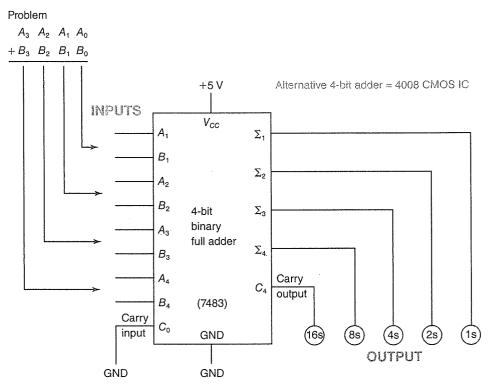

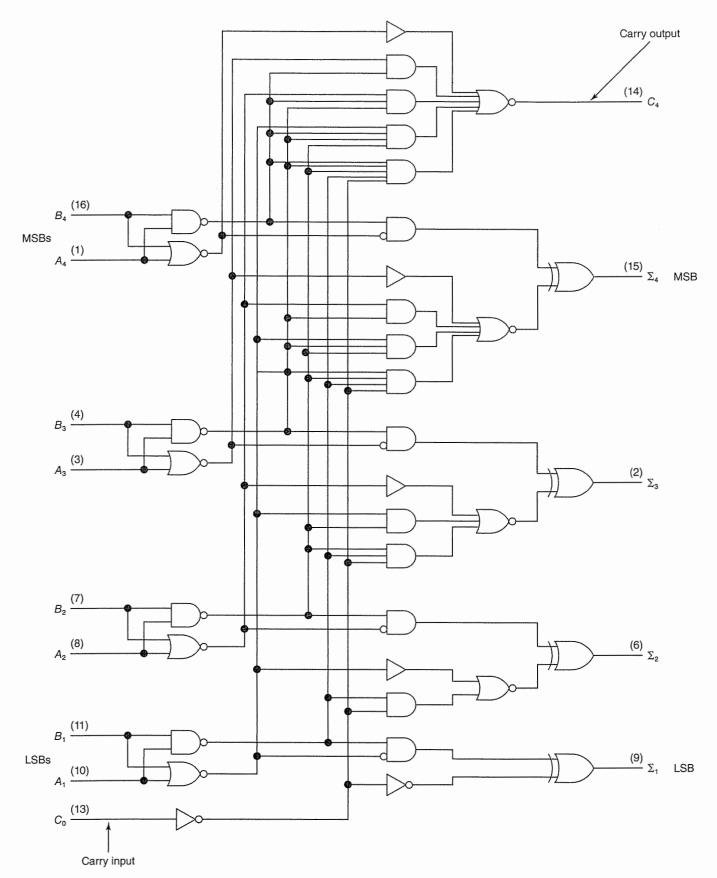

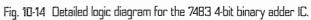

| 10-7    | IC Adders                            |

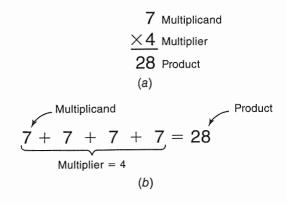

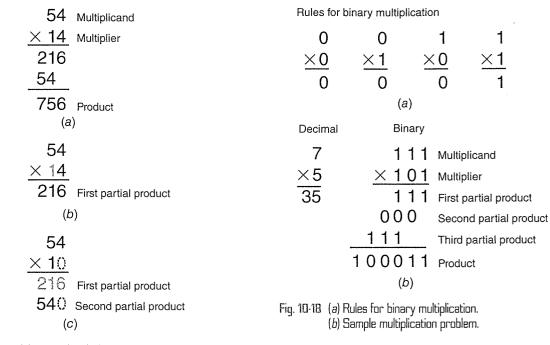

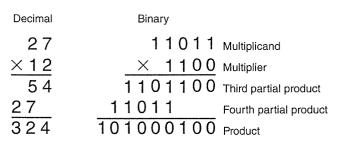

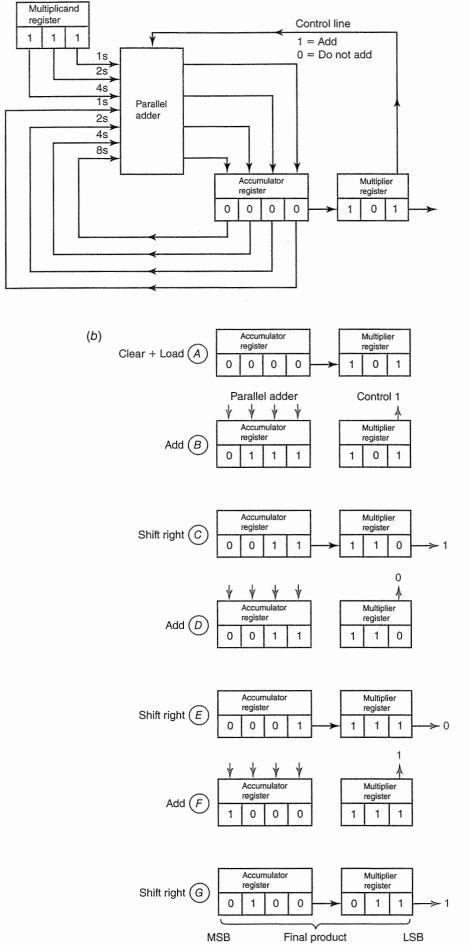

| 10-8    | Binary Multiplication                |

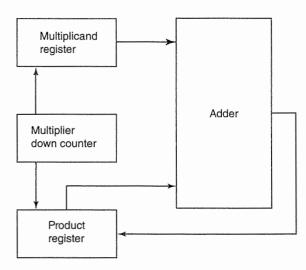

| 10-9    | Binary Multipliers                   |

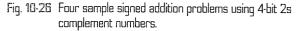

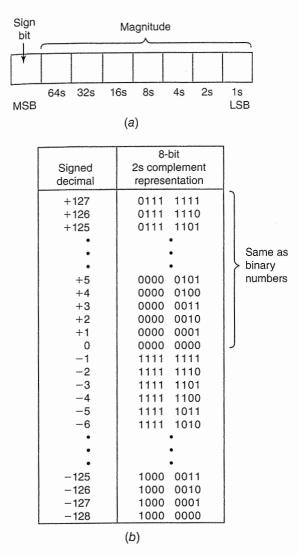

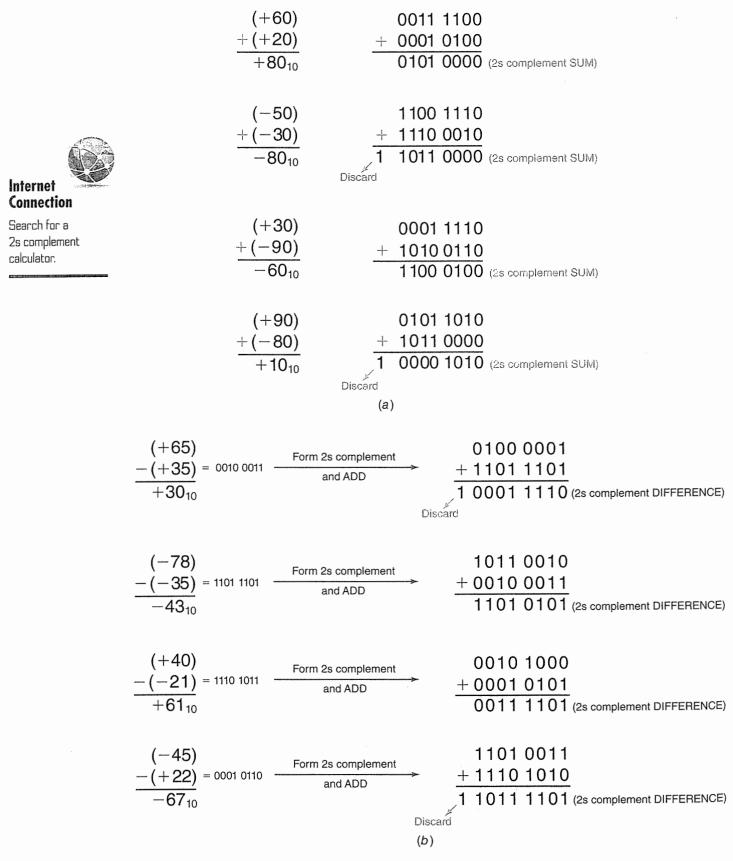

| 10-10   | 2s Complement Notation, Addition,    |

|         | and Subtraction                      |

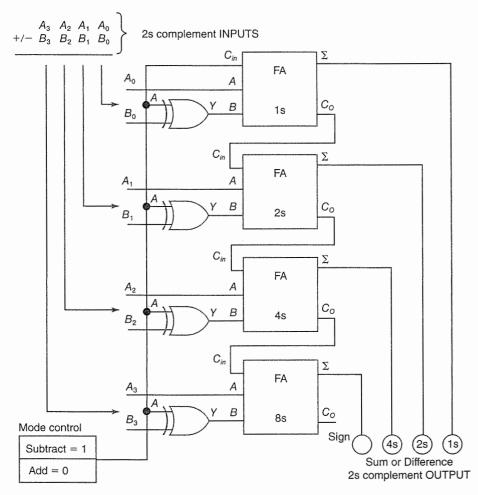

| 10-11   | 2s Complement Adders/Subtractors 353 |

| 10-12   | Troubleshooting a Full Adder 355     |

| Summa   | ry                                   |

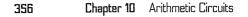

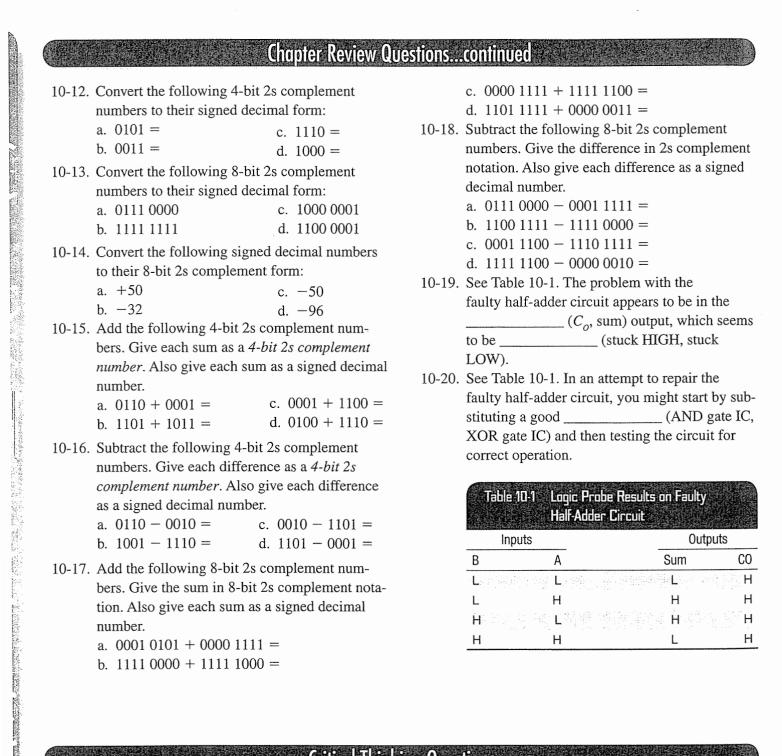

| Chapter | r Review Questions 357               |

|         |                                      |

vi

And Andrea Kardina and Andrea Andrea. The analysis of the a

|                                                                                                                       | I Thinking Questions                                                                                                                                                                                                                                                                                          |                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Chapte                                                                                                                |                                                                                                                                                                                                                                                                                                               | 361                                                                                                                        |

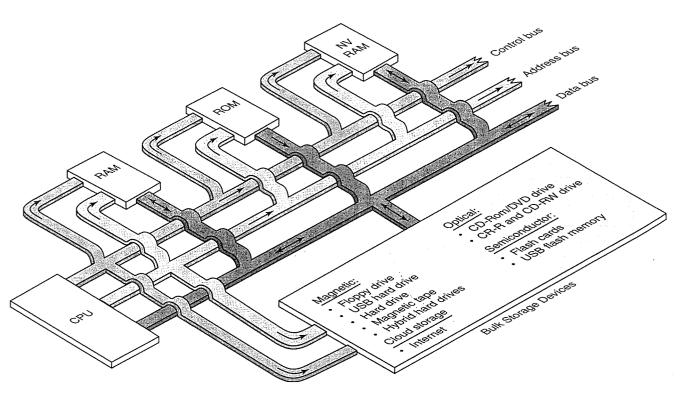

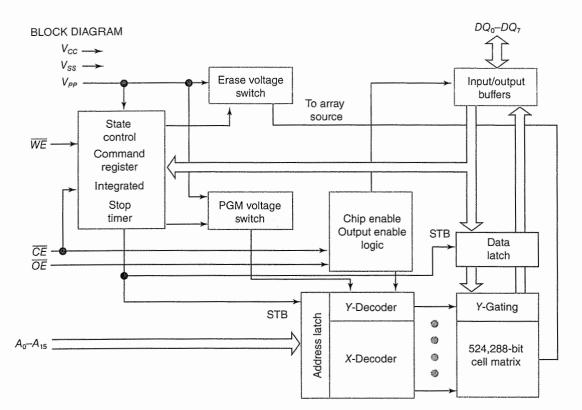

| 11-1                                                                                                                  | Overview of Memory                                                                                                                                                                                                                                                                                            | 362                                                                                                                        |

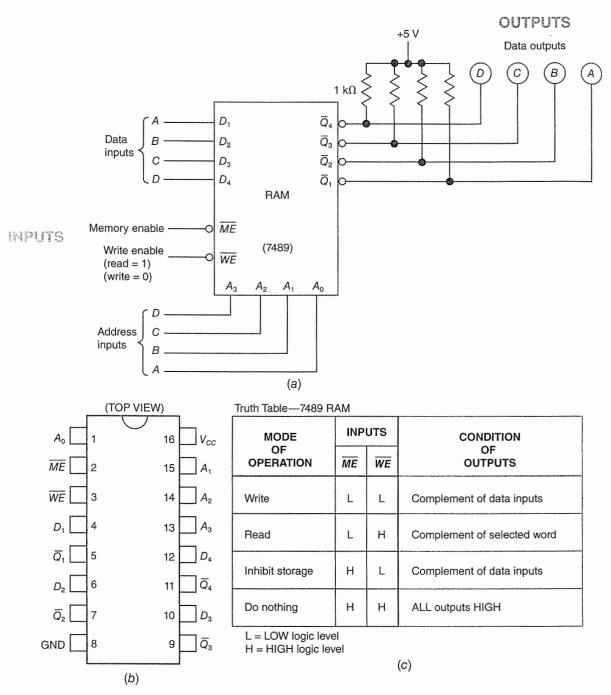

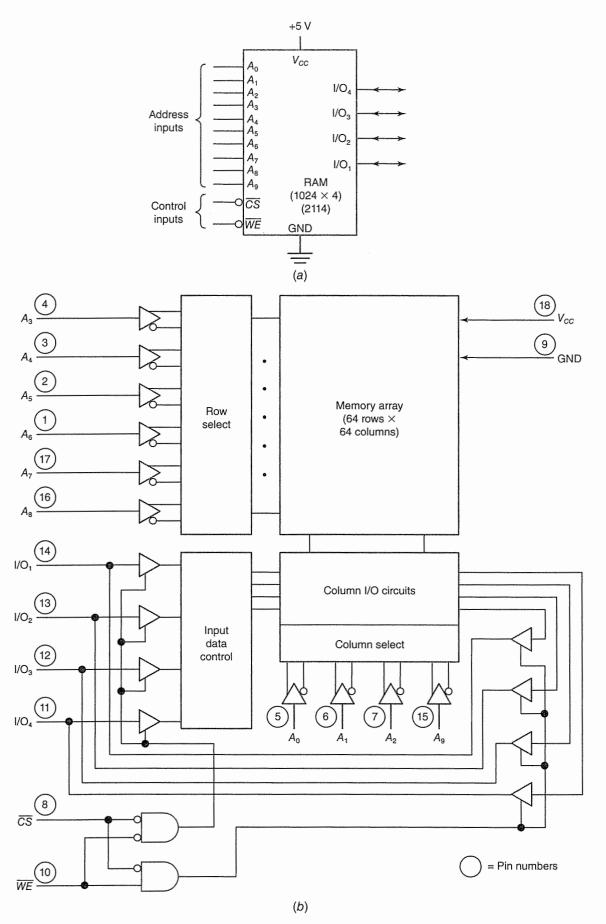

| 11-2                                                                                                                  | Random-Access Memory (RAM)                                                                                                                                                                                                                                                                                    |                                                                                                                            |

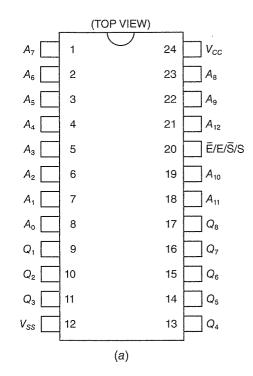

| 11-3                                                                                                                  | Static RAM ICs.                                                                                                                                                                                                                                                                                               |                                                                                                                            |

| 11-4                                                                                                                  | Using a SRAM                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

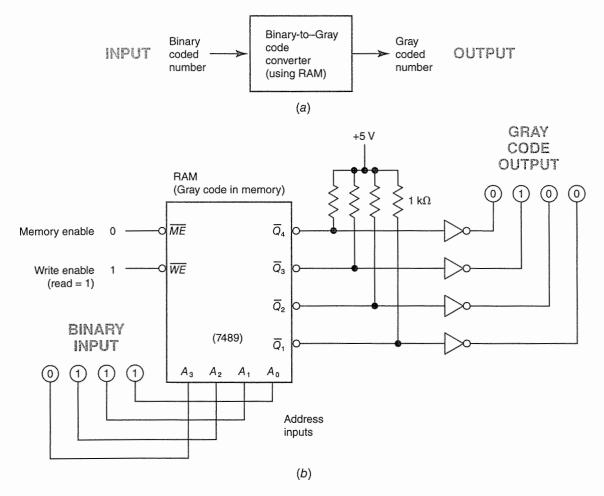

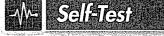

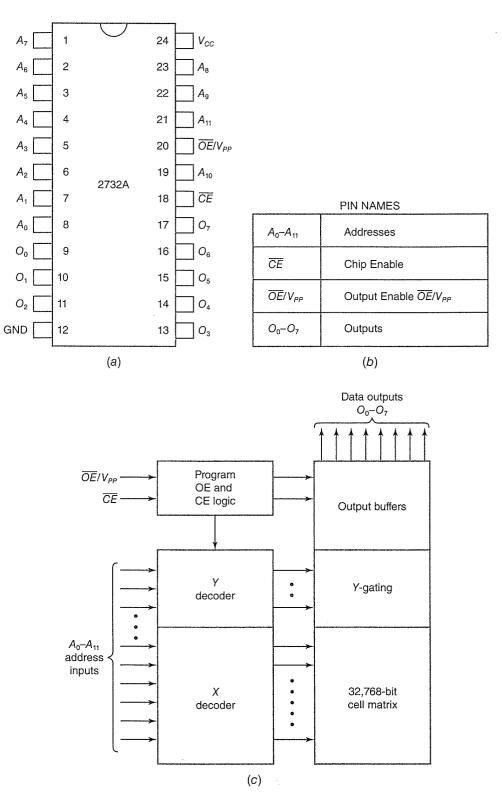

| 11-5                                                                                                                  | Read-Only Memory (ROM)                                                                                                                                                                                                                                                                                        |                                                                                                                            |

| 11-6                                                                                                                  | Using a ROM                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

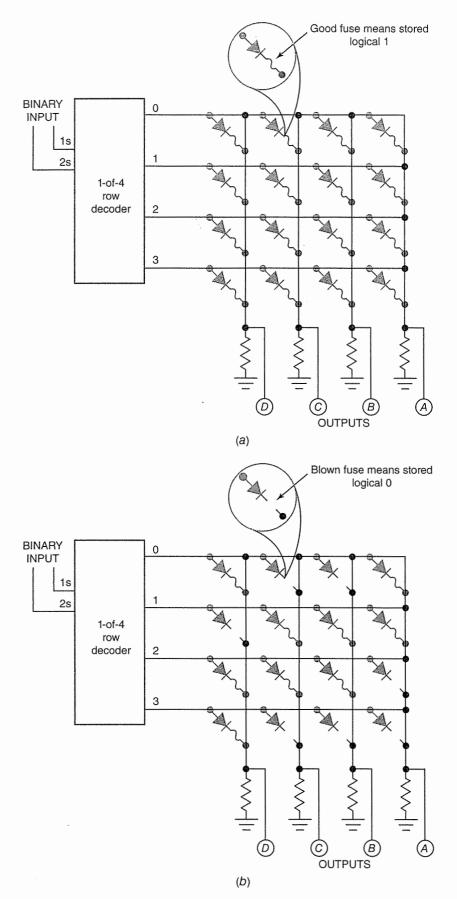

| 11-7                                                                                                                  | Programmable Read-Only Memory                                                                                                                                                                                                                                                                                 |                                                                                                                            |

|                                                                                                                       | [PROM]                                                                                                                                                                                                                                                                                                        | 377                                                                                                                        |

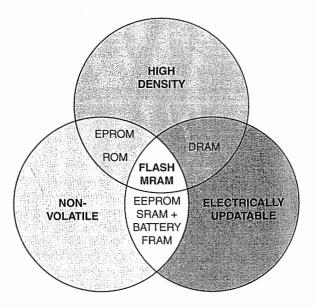

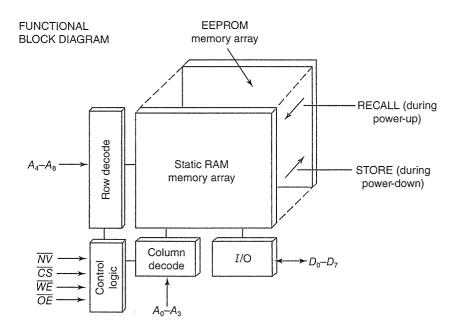

| 11-8                                                                                                                  | Nonvolatile Read/Write Memory                                                                                                                                                                                                                                                                                 | 381                                                                                                                        |

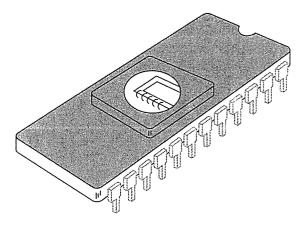

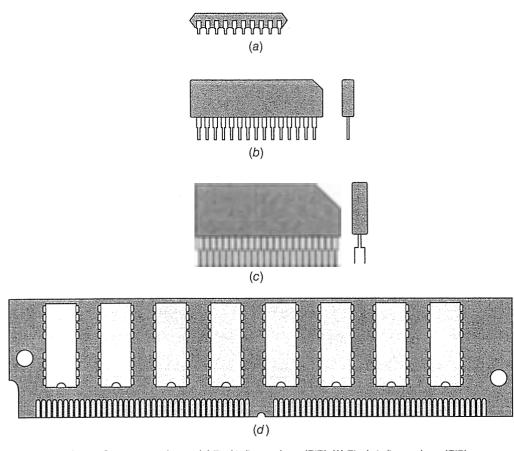

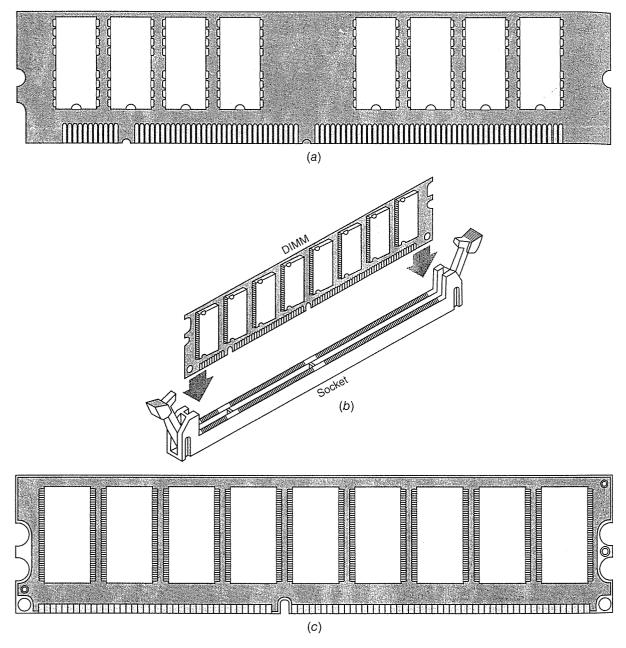

| 11-9                                                                                                                  | Memory Packaging                                                                                                                                                                                                                                                                                              | 384                                                                                                                        |

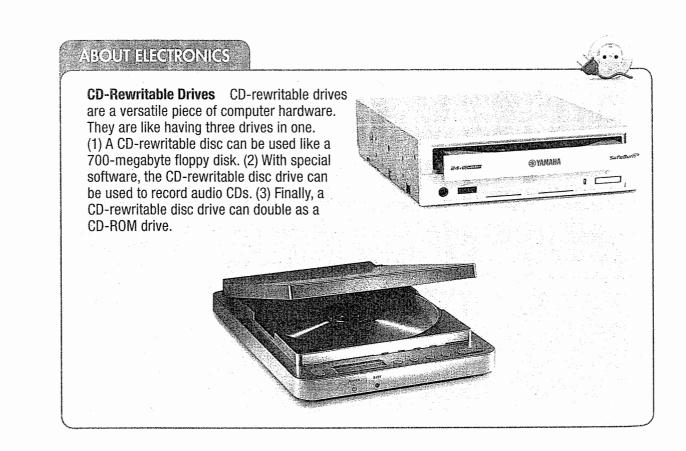

| 11-10                                                                                                                 | Computer Bulk Storage Devices                                                                                                                                                                                                                                                                                 |                                                                                                                            |

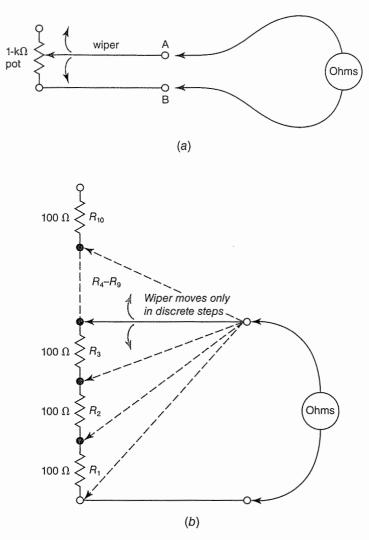

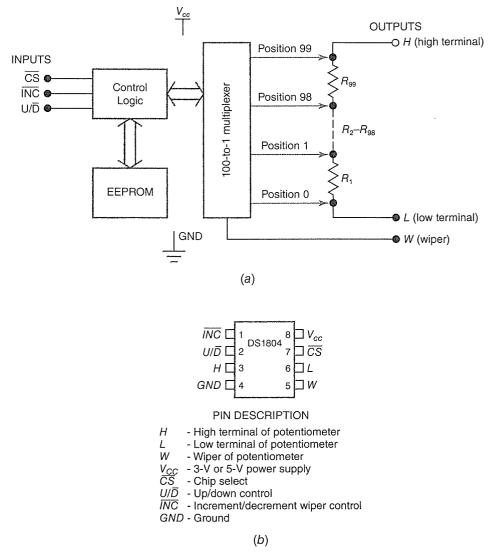

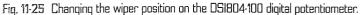

| 11 - 11                                                                                                               | Digital Potentiometer: Using NV Memory                                                                                                                                                                                                                                                                        |                                                                                                                            |

|                                                                                                                       | ary                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

|                                                                                                                       | er Review Questions                                                                                                                                                                                                                                                                                           |                                                                                                                            |

|                                                                                                                       | 1 Thinking Questions                                                                                                                                                                                                                                                                                          |                                                                                                                            |

| Answe                                                                                                                 | ers to Self-Tests                                                                                                                                                                                                                                                                                             | 401                                                                                                                        |

| -                                                                                                                     |                                                                                                                                                                                                                                                                                                               |                                                                                                                            |

| Chapte                                                                                                                | r 12 Simple Digital Systems                                                                                                                                                                                                                                                                                   | 403                                                                                                                        |

| Chapte<br>12-1                                                                                                        |                                                                                                                                                                                                                                                                                                               |                                                                                                                            |

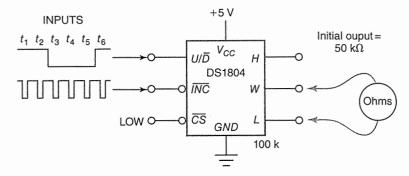

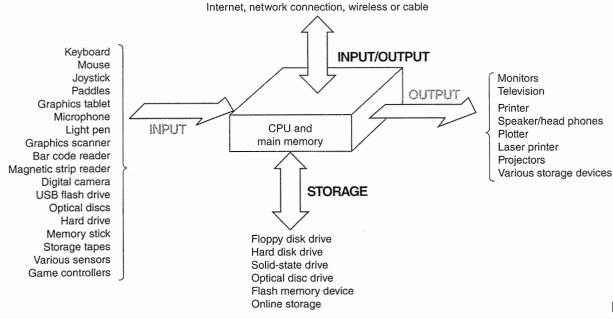

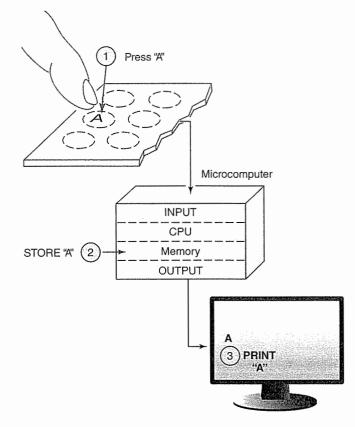

| <u> </u>                                                                                                              | Elements of a System                                                                                                                                                                                                                                                                                          | 403                                                                                                                        |

| 12-1                                                                                                                  | Elements of a System                                                                                                                                                                                                                                                                                          | 403<br>406                                                                                                                 |

| 12-1<br>12-2                                                                                                          | Elements of a System                                                                                                                                                                                                                                                                                          | 403<br>406<br>407                                                                                                          |

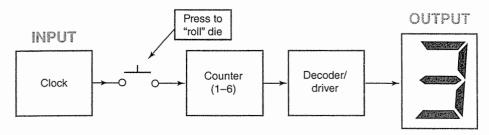

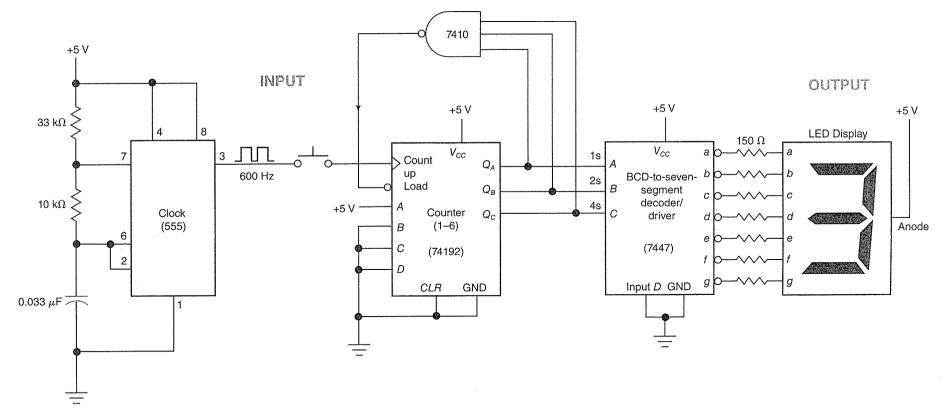

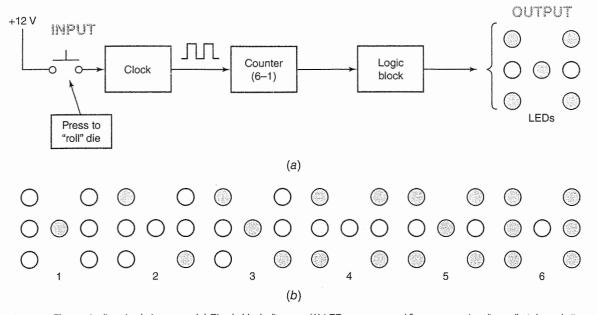

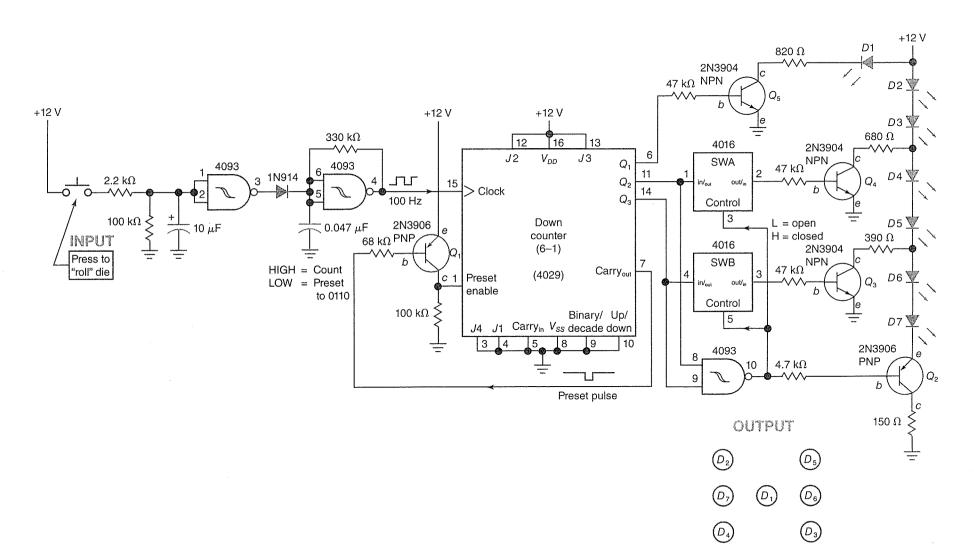

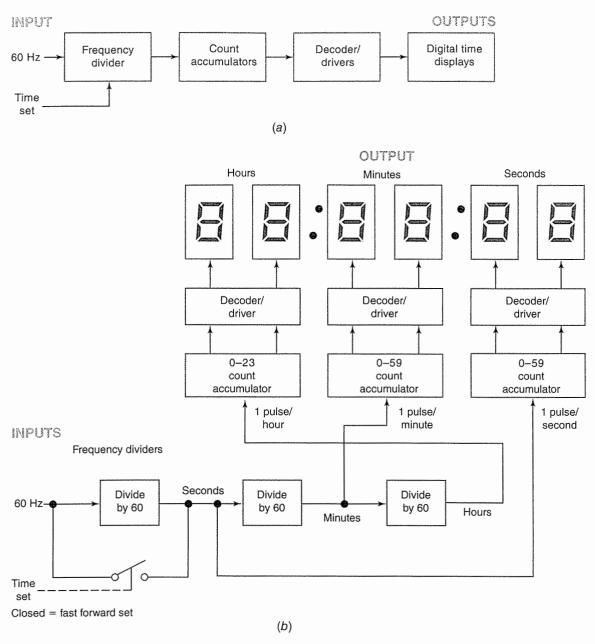

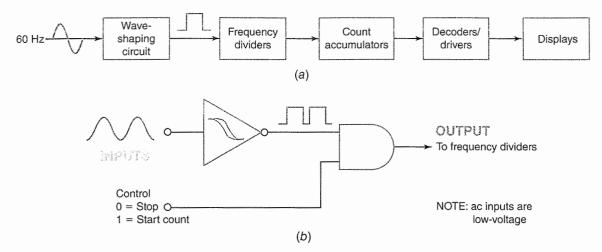

| 12-1<br>12-2<br>12-3                                                                                                  | Elements of a System                                                                                                                                                                                                                                                                                          | 403<br>406<br>407<br>412                                                                                                   |

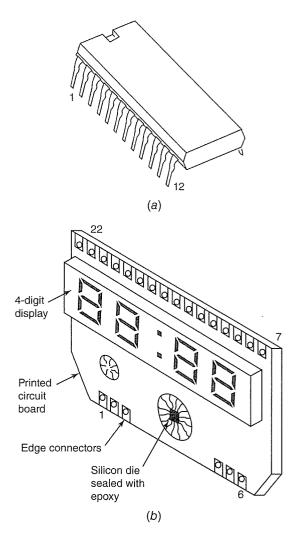

| 12-1<br>12-2<br>12-3<br>12-4                                                                                          | Elements of a System                                                                                                                                                                                                                                                                                          | 403<br>406<br>407<br>412<br>415                                                                                            |

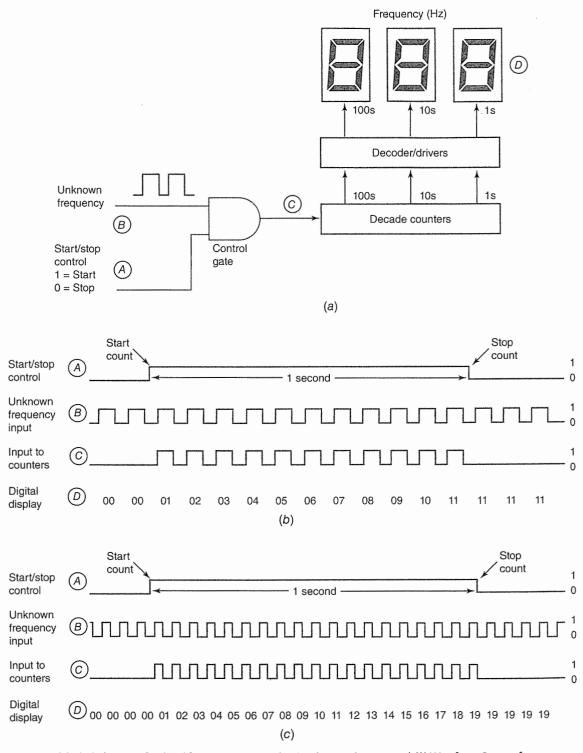

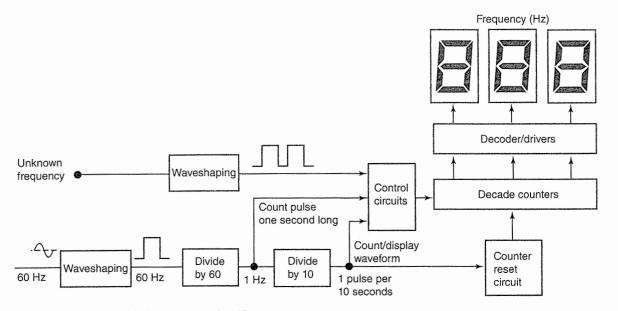

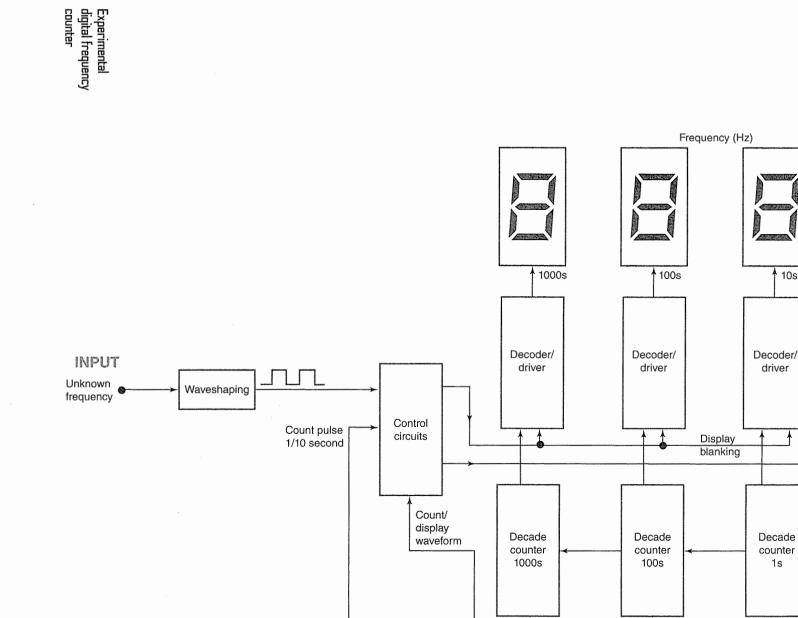

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5                                                                                  | Elements of a System                                                                                                                                                                                                                                                                                          | 403<br>406<br>407<br>412<br>415<br>419<br>423                                                                              |

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6                                                                          | Elements of a System                                                                                                                                                                                                                                                                                          | 403<br>406<br>407<br>412<br>415<br>419<br>423<br>426                                                                       |

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9                                                  | Elements of a System                                                                                                                                                                                                                                                                                          | 403<br>406<br>407<br>412<br>415<br>419<br>423<br>426<br>432                                                                |

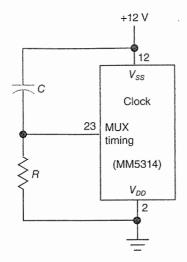

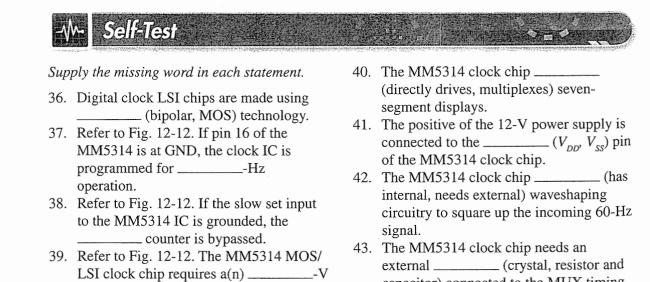

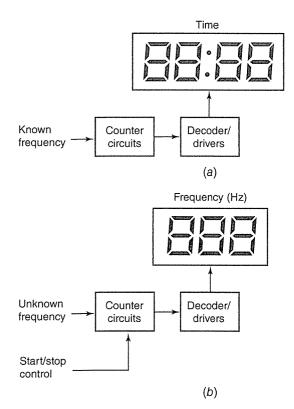

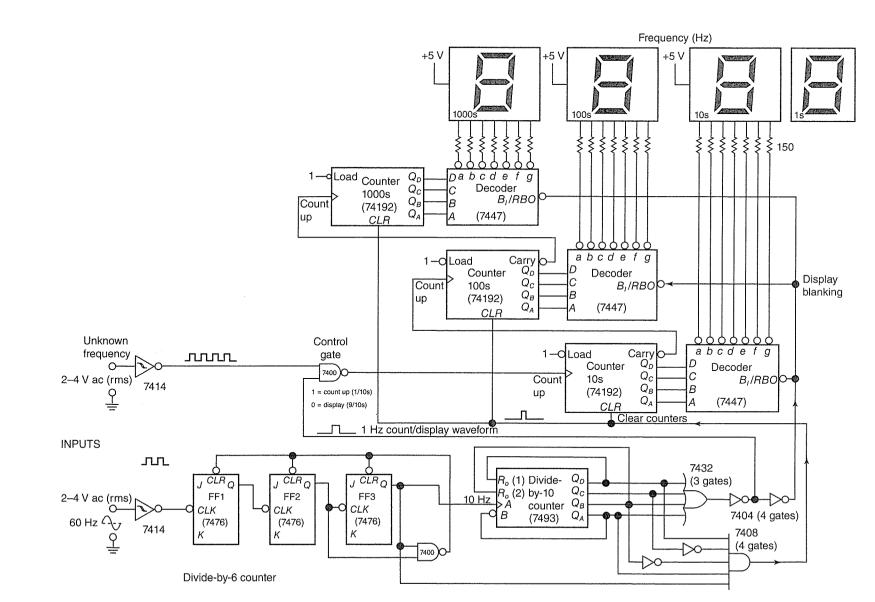

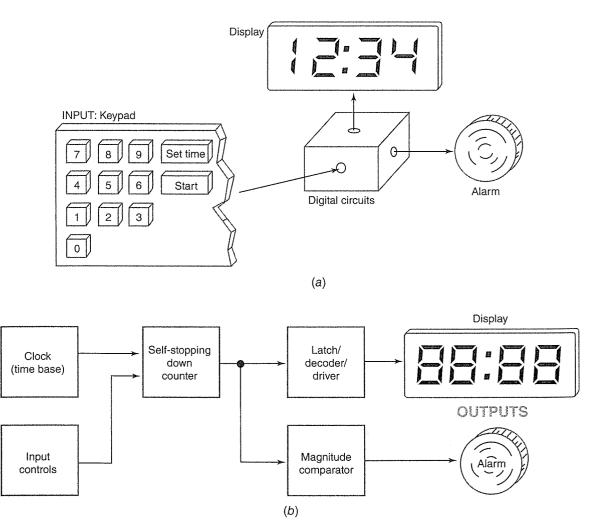

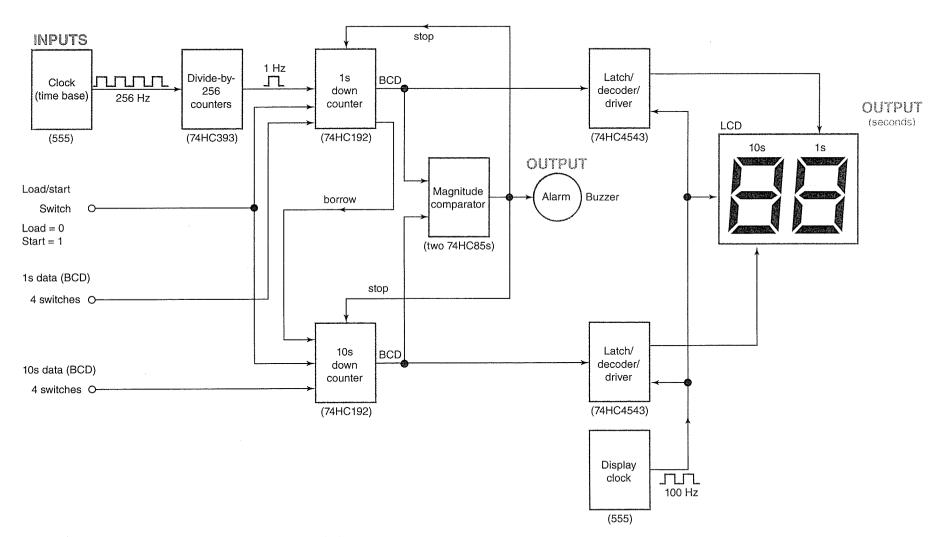

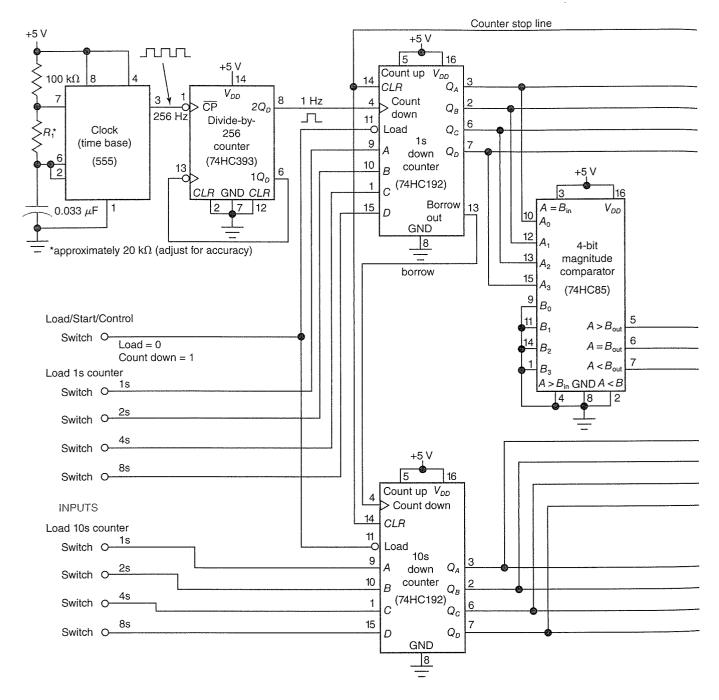

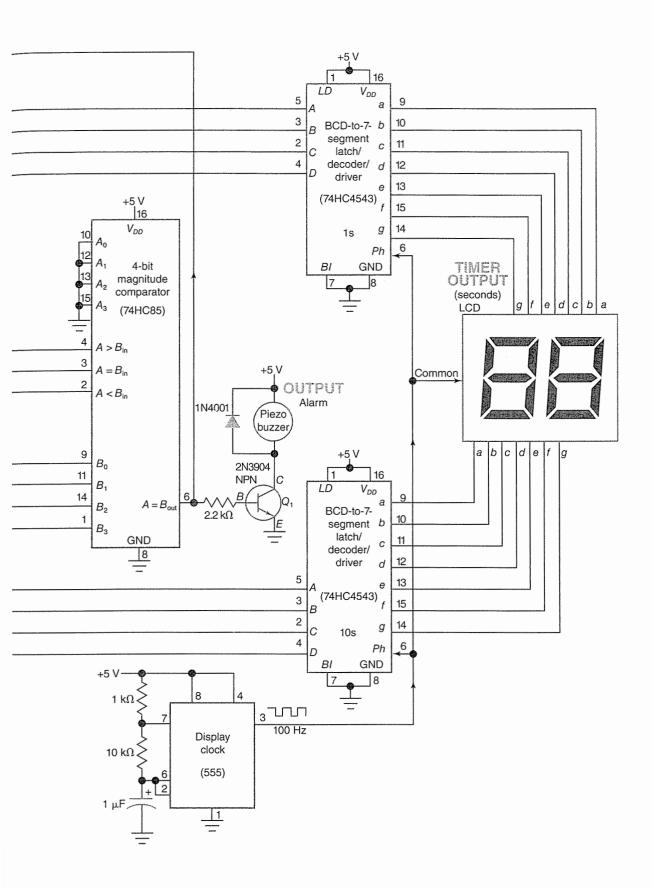

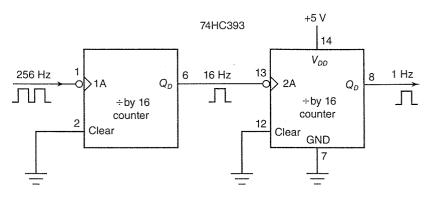

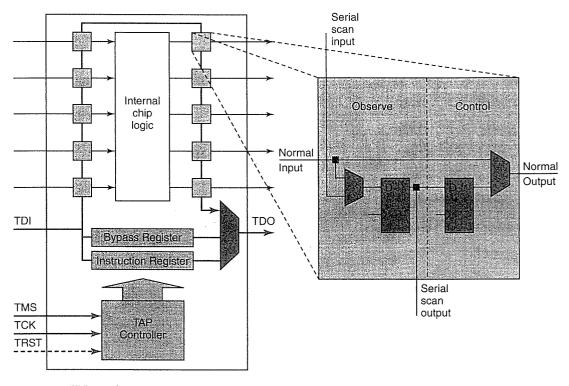

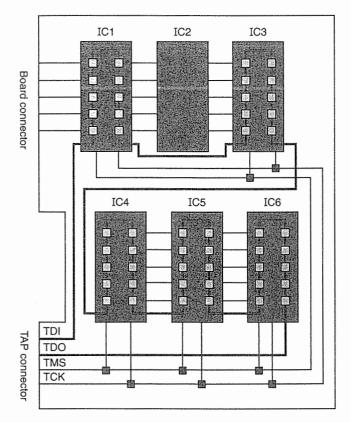

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10                                         | Elements of a System                                                                                                                                                                                                                                                                                          | 403<br>406<br>407<br>412<br>415<br>419<br>423<br>426<br>432<br>437                                                         |

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>Summa                                | Elements of a System                                                                                                                                                                                                                                                                                          | 403<br>406<br>407<br>412<br>415<br>419<br>423<br>426<br>432<br>437<br>441                                                  |

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>Summa<br>Chapter                     | Elements of a System<br>A Digital System on an IC<br>Digital Games<br>The Digital Clock<br>The LSI Digital Clock<br>The Frequency Counter<br>An Experimental Frequency Counter<br>LCD Timer with Alarm.<br>Simple Distance Sensing<br>JTAG/Boundary Scan<br>er Review Questions.                              | 403<br>406<br>407<br>412<br>415<br>419<br>423<br>426<br>432<br>437<br>441<br>441                                           |

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>Summa<br>Chaptee<br>Critica          | Elements of a System                                                                                                                                                                                                                                                                                          | 403<br>406<br>407<br>412<br>415<br>419<br>423<br>426<br>432<br>437<br>441<br>441<br>443                                    |

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>Summa<br>Chaptee<br>Critica          | Elements of a System<br>A Digital System on an IC<br>Digital Games<br>The Digital Clock<br>The LSI Digital Clock<br>The Frequency Counter<br>An Experimental Frequency Counter<br>LCD Timer with Alarm.<br>Simple Distance Sensing<br>JTAG/Boundary Scan<br>er Review Questions.                              | 403<br>406<br>407<br>412<br>415<br>419<br>423<br>426<br>432<br>437<br>441<br>441<br>443                                    |

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>Summa<br>Chaptee<br>Critica          | Elements of a System<br>A Digital System on an IC<br>Digital Games<br>The Digital Clock<br>The LSI Digital Clock<br>The Frequency Counter<br>An Experimental Frequency Counter<br>LCD Timer with Alarm<br>Simple Distance Sensing<br>JTAG/Boundary Scan<br>ary<br>er Review Questions<br>1 Thinking Questions | 403<br>406<br>407<br>412<br>415<br>419<br>423<br>426<br>432<br>437<br>441<br>441<br>443                                    |

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>Summa<br>Chaptee<br>Critica<br>Answe | Elements of a System                                                                                                                                                                                                                                                                                          | 403<br>406<br>407<br>412<br>415<br>419<br>423<br>426<br>432<br>437<br>441<br>443<br>444<br>443<br>444<br>445               |

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>Summ<br>Chapte<br>Critica<br>Answe   | Elements of a System<br>A Digital System on an IC<br>Digital Games<br>The Digital Clock<br>The LSI Digital Clock<br>The Frequency Counter<br>An Experimental Frequency Counter<br>LCD Timer with Alarm<br>Simple Distance Sensing<br>JTAG/Boundary Scan<br>ary<br>er Review Questions<br>1 Thinking Questions | 403<br>406<br>407<br>412<br>415<br>419<br>423<br>426<br>432<br>437<br>441<br>441<br>441<br>443<br>444<br>444<br>445<br>445 |

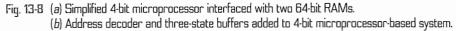

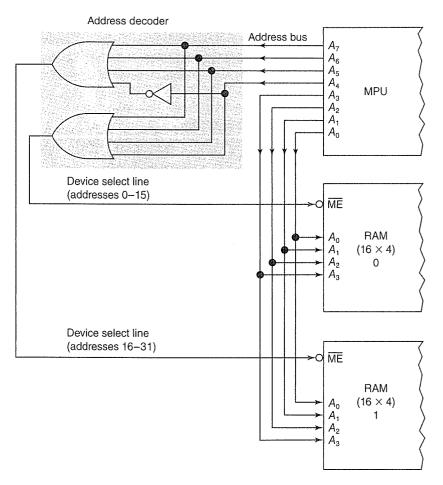

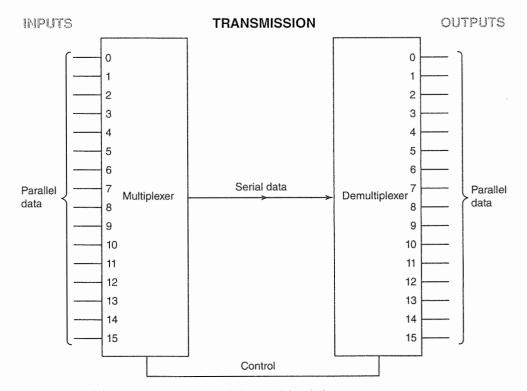

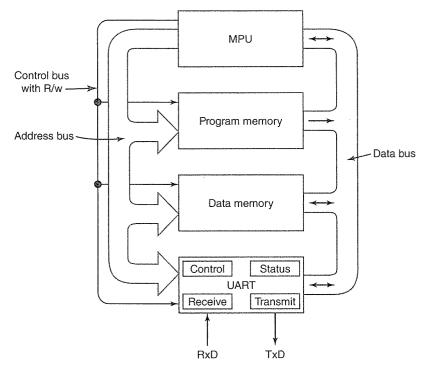

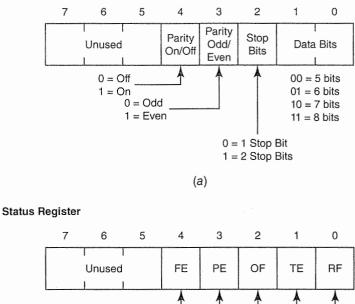

| 13-4    | Microcomputer Address Decoding 454         |

|---------|--------------------------------------------|

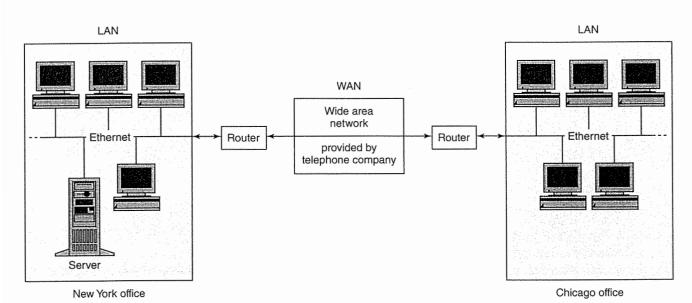

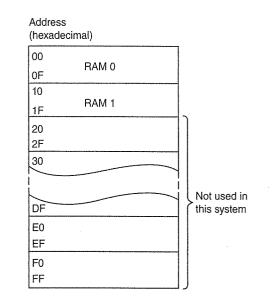

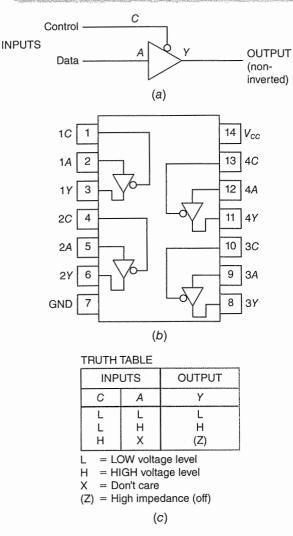

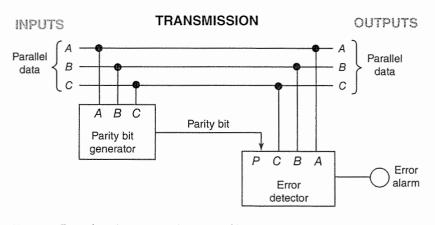

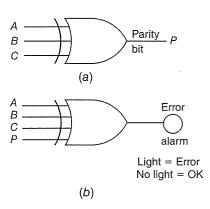

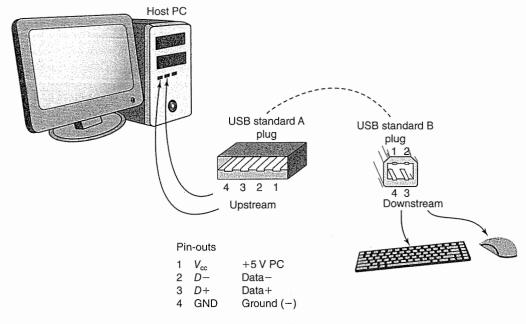

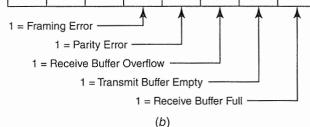

| 13-5    | Data Transmission                          |

| 13-6    | Detecting Errors in Data Transmissions 461 |

| 13-7    | Data Transmission in a Computer System 464 |

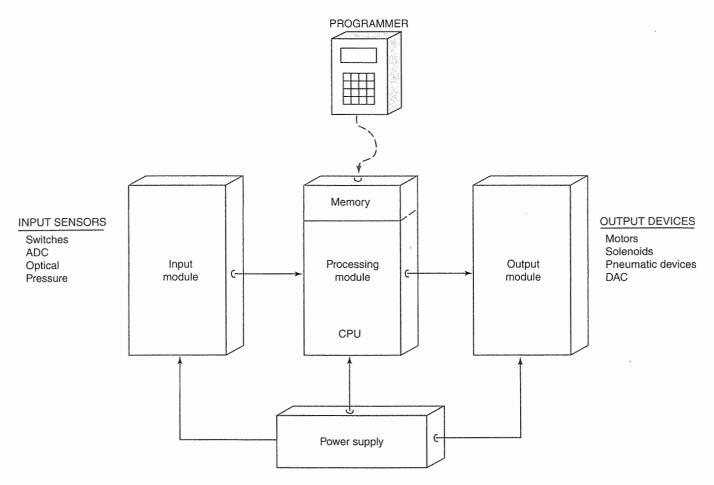

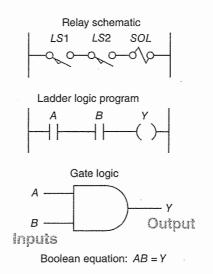

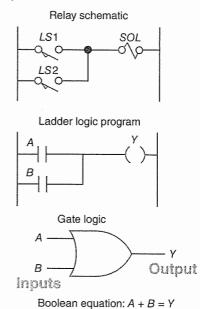

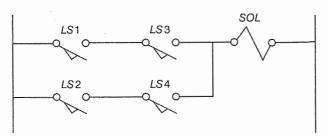

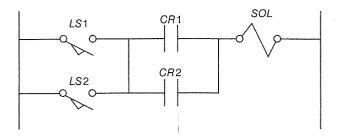

| 13-8    | Programmable Logic Controllers (PLCs) 469  |

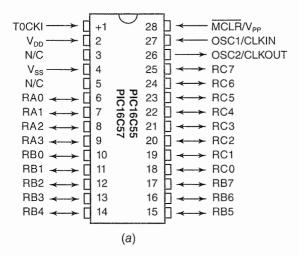

| 13-9    | Microcontrollers 473                       |

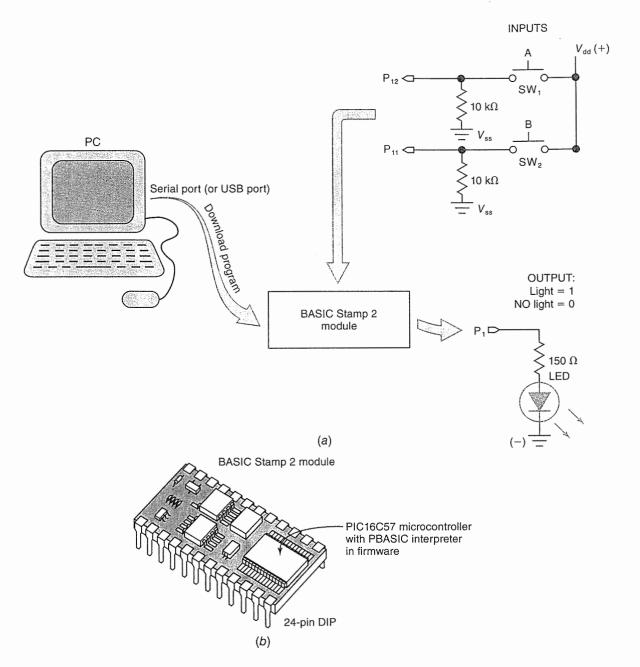

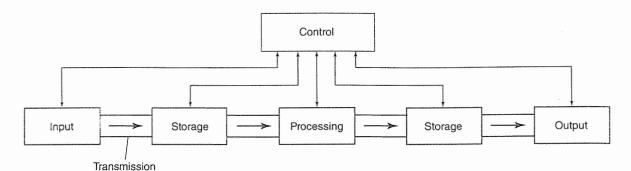

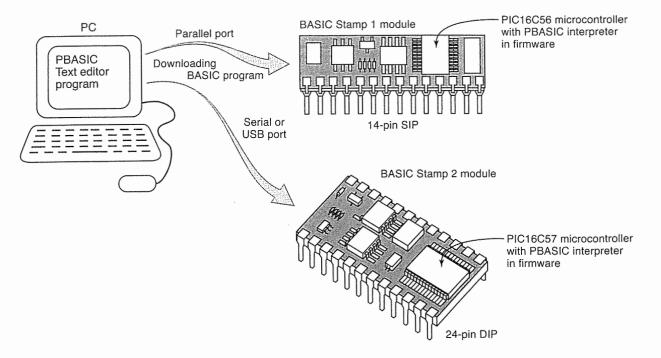

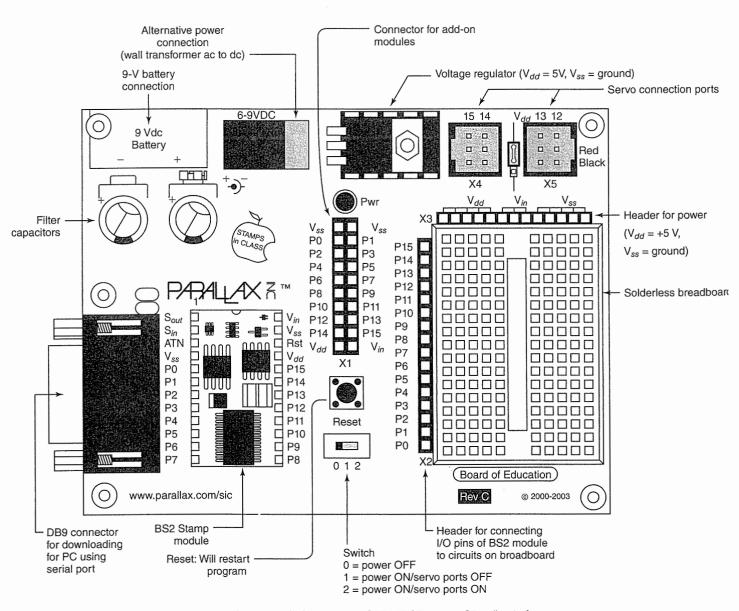

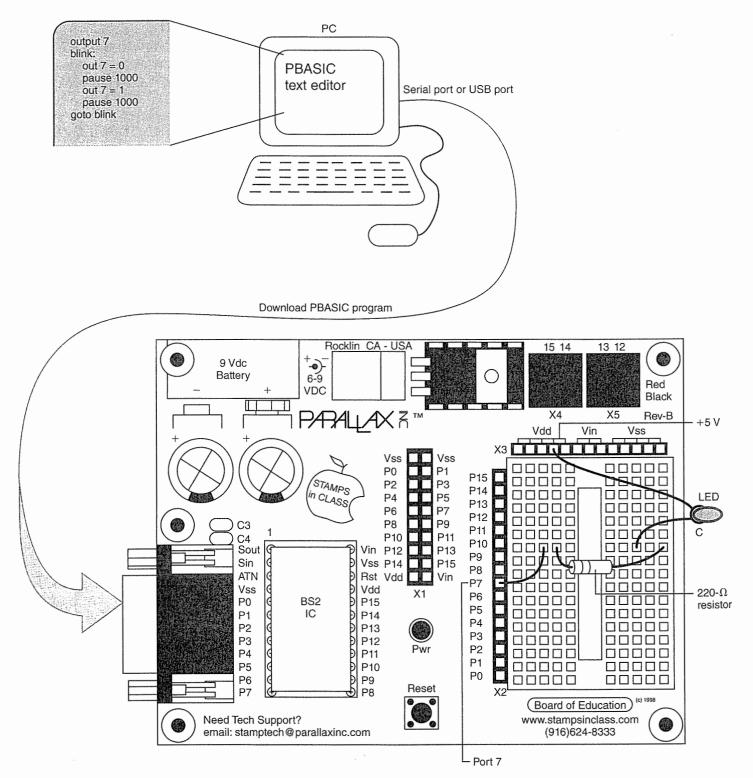

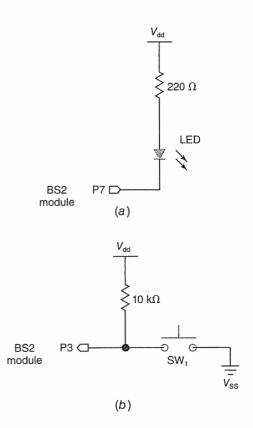

| 13-10   | The BASIC Stamp Microcontroller            |

|         | Modules 475                                |

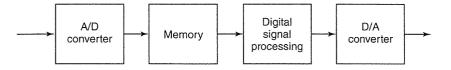

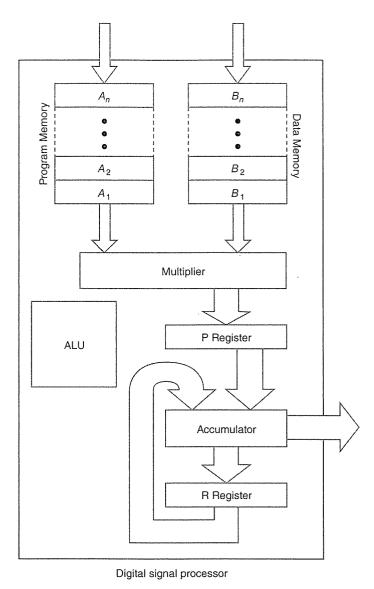

| 13-11   | Digital Signal Processing 482              |

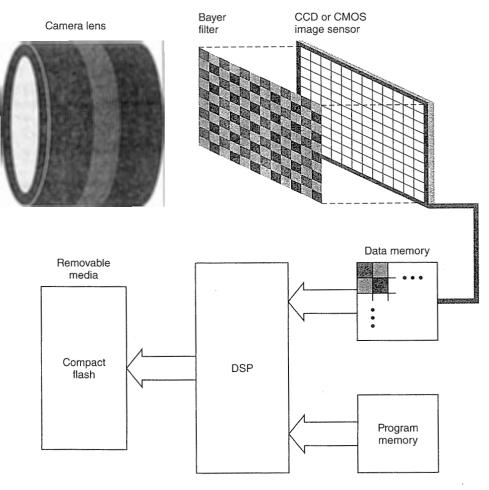

| 13-12   | DSP in a Digital Camera                    |

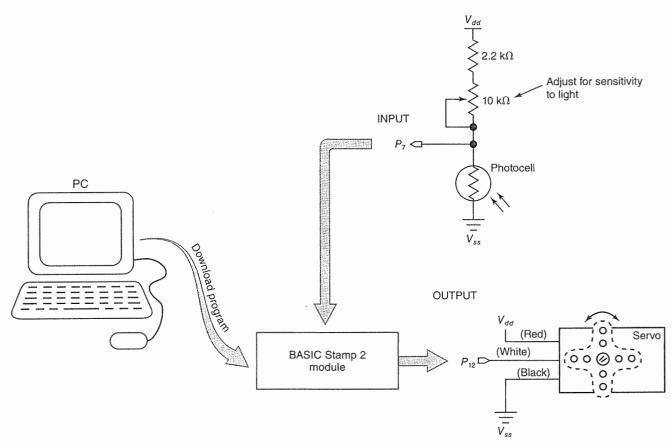

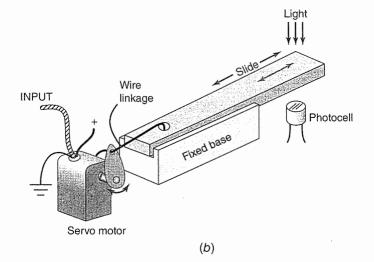

| 13-13   | Microcontroller: Photo Input and Servo     |

|         | Motor Output                               |

| Summa   | ry                                         |

| Chapter | Review Questions                           |

|         | Thinking Questions                         |

|         | rs to Self-Tests                           |

|         |                                            |

| Chapter | 14 Connecting with Analog Devices 499      |

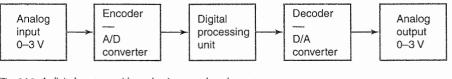

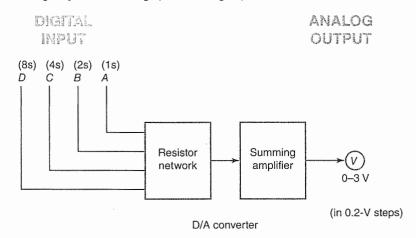

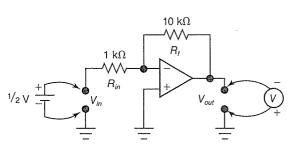

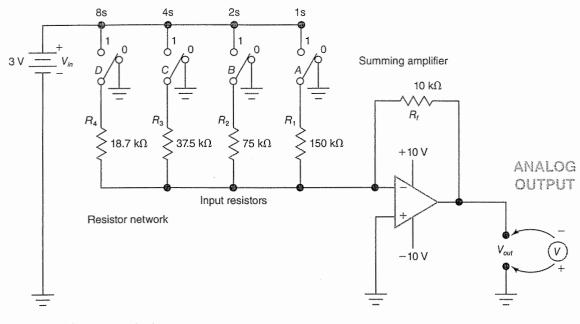

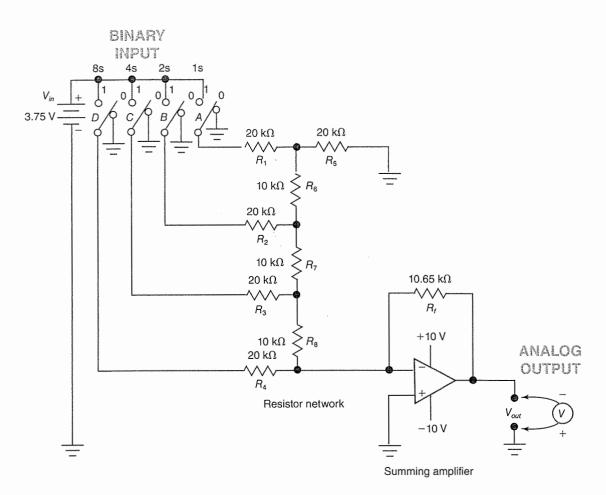

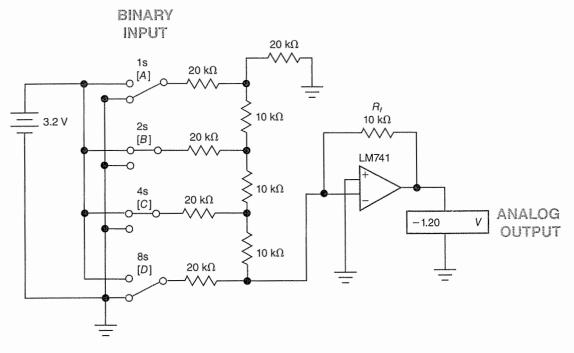

| 14-1    | D/A Conversion                             |

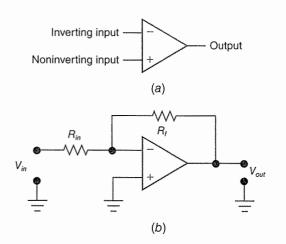

| 14-2    | Operational Amplifiers 501                 |

| 14-3    | A Basic D/A Converter                      |

| 14-4    | Ladder-Type D/A Converters 504             |

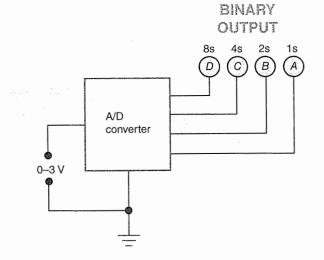

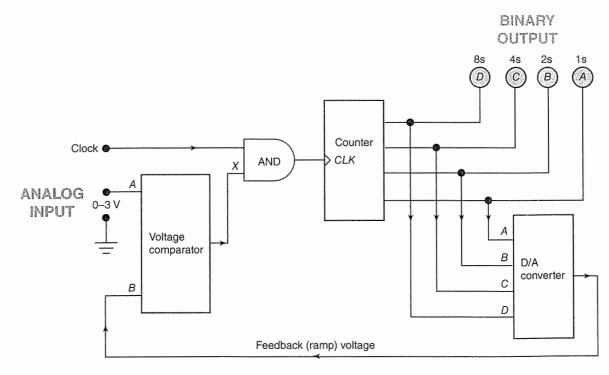

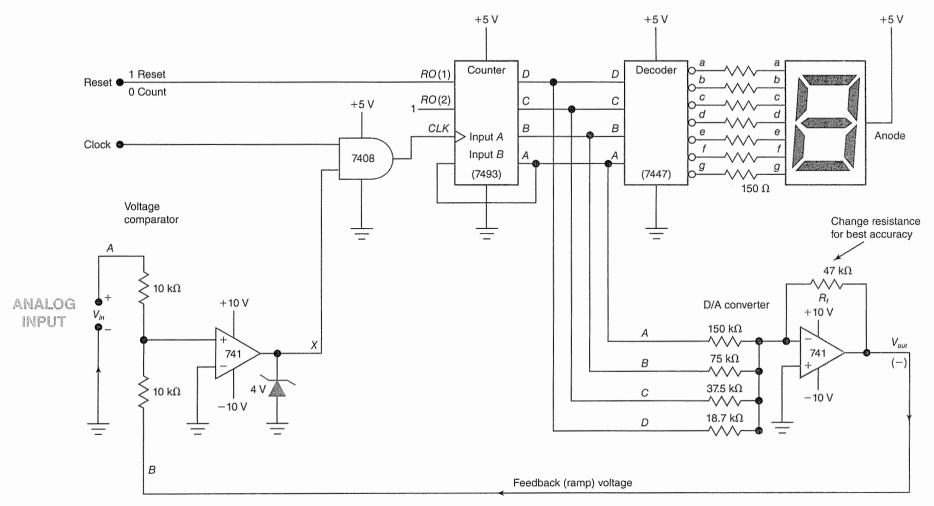

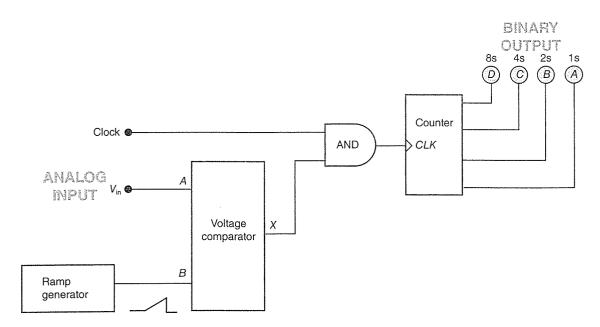

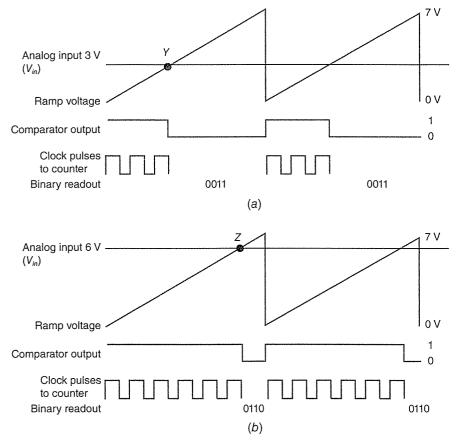

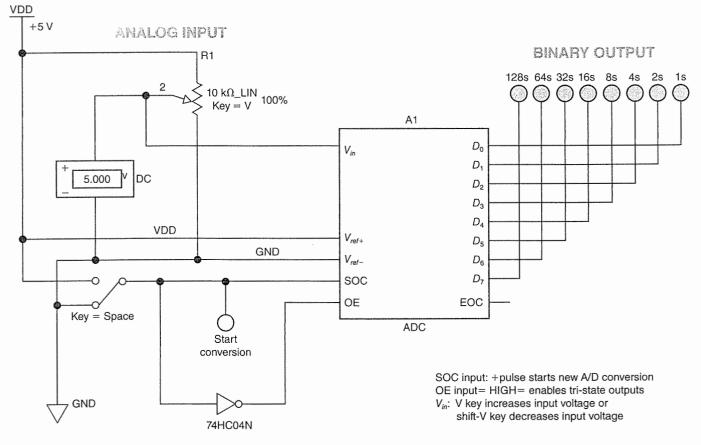

| 14-5    | An A/D Converter                           |

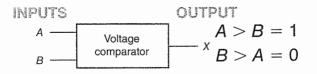

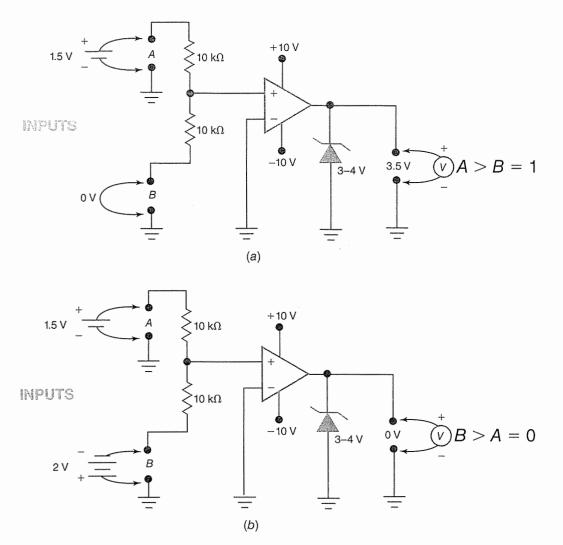

| 14-6    | Voltage Comparators 508                    |

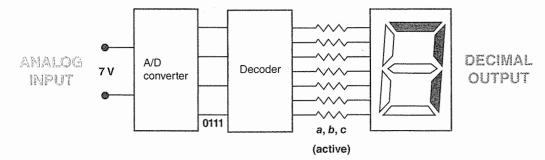

| 14-7    | An Elementary Digital Voltmeter            |

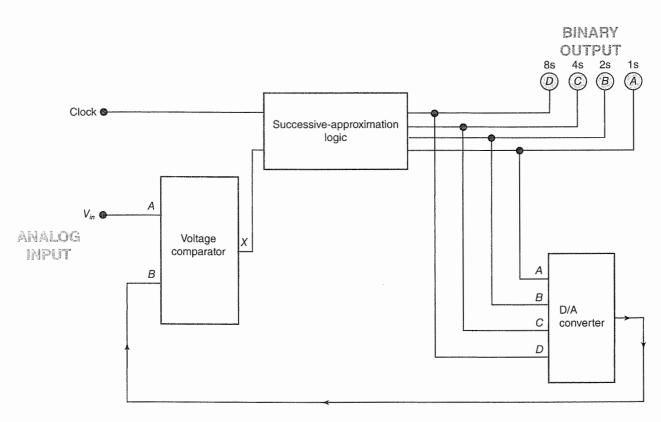

| 14-8    | Other A/D Converters                       |

| 14-9    | A/D Converter Specifications 516           |

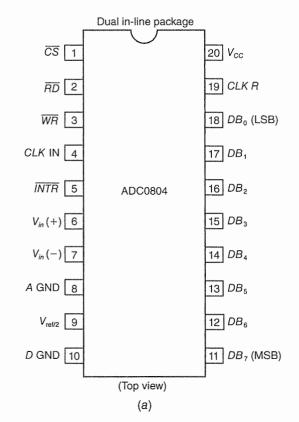

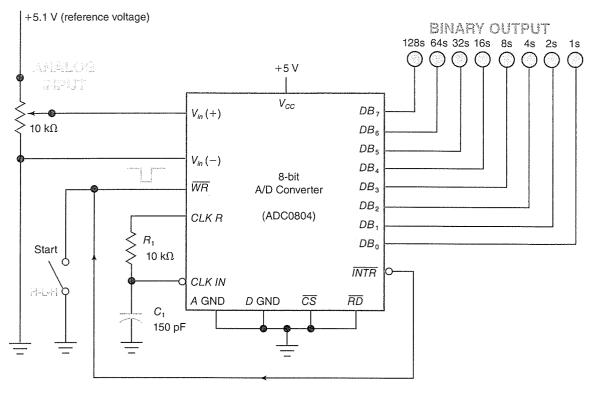

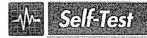

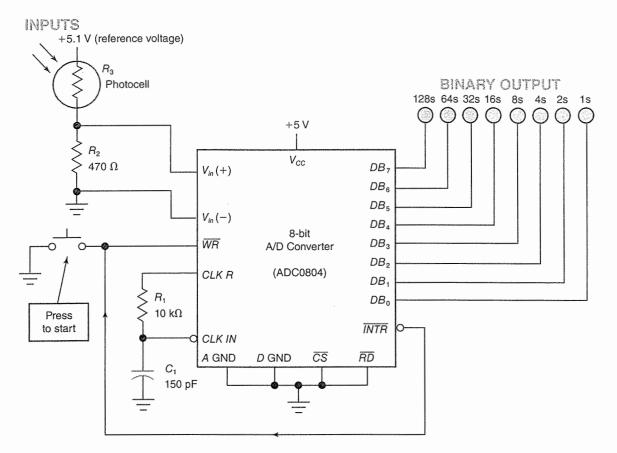

| 14-10   | An A/D Converter IC 517                    |

| 14-11   | Digital Light Meter                        |

| 14-12   | Digitizing Temperature                     |

| Summa   | ry                                         |

|         | Review Questions                           |

|         | Thinking Questions                         |

|         | rs to Self-Tests 528                       |

|         |                                            |

| Append  | 8                                          |

| Append  | lix B 2s Complement Conversions 535        |

| Glossar | y of Terms and Symbols 536                 |

|         |                                            |

|         |                                            |

|         |                                            |

ander and the second state of the state of the second state of the second state of the state of the second state

# Editor's Foreword

The McGraw-Hill Education Trade and Technology list has been designed to provide entry-level competencies in a wide range of occupations in the electrical and electronics fields. It consists of coordinated instructional materials designed especially for career-oriented students. A textbook, an experiments manual, and online resources support each major subject area covered in the series. All of these focus on theory, practice, applications, and experiences necessary for those preparing to enter technical careers.

There are two fundamental considerations in the preparation of a text like *Digital Electronics: Principles and Applications:* the needs for the learner and the needs of the employer. This text meets those needs in expert fashion. The authors and editors have drawn upon their broad teaching and technical experiences to accurately interpret and meet the needs of the student. The needs of business and industry have been identified through personal interviews, industry publications, government occupational trend reports, and reports by industry associations.

The processes used to produce and refine the series have been ongoing. Technological change is rapid, and the content has been revised to focus on current trends. Refinements in pedagogy have been defined and implemented based on classroom testing and feedback from students and instructors using the series. Every effort has been made to offer the best possible learning materials. These include animated PowerPoint presentations, circuit files for simulation, a test generator with correlated test banks, dedicated websites for both students and instructors, and basic instrumentation labs. All of these are well coordinated and have been prepared by the author.

The widespread acceptance of *Digital Electronics: Principles and Applications* and the positive feedback from users confirm the basic soundness in content and design of all the components as well as their effectiveness as teaching and learning tools. Instructors will find the texts and manuals in each of the subject areas logically structured, well paced, and developed around a framework of modern objectives. Students will find the materials to be readable, lucidly illustrated, and interesting. They will also find a generous amount of self-study materials, review items, and examples to help them determine their own progress.

Both the initial and ongoing success of this text and others with the McGraw-Hill Trade and Technology list are due in large part to the wisdom and vision of Gordon Rockmaker, who was a magical combination of editor, writer, teacher, electrical engineer, and friend. The publisher and editor welcome comments and suggestions from instructors and students using this series.

#### Charles A. Schuler, Project Editor

# Basic Skills in Electricity and Electronics

Charles A. Schuler, Project Editor

### New Editions in This Series

*Electricity: Principles and Applications, Eighth Edition, Richard J. Fowler Electronics: Principles and Applications, Eighth Edition, Charles A. Schuler*

# Preface

Digital Electronics: Principles and Applications, eighth edition, is an easy-to-read introductory text for students new to the field of digital electronics. Providing entry-level knowledge and skills for a wide range of occupations is the goal of this textbook and its ancillary materials. Prerequisites are general math and introductory electricity/electronics. Binary math, Boolean concepts, simple programming, and various codes are introduced and explained as needed. Concepts are connected to practical applications, and a systems approach is followed that reflects current practice in industry. Earlier editions of the text have been used successfully in a wide range of programs: electronic technology, electrical trades and apprenticeship training, computer repair, communications electronics, and computer science, to name a few. This concise and practical text can be used in any program needing a quick and readable overview of digital principles.

# New to this Edition

### Chapter 1

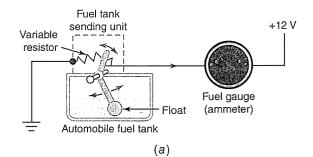

- Digital applications, including automotive fuel indicators, vehicle speed sensors, and engine control module.

- A new section on where digital circuit applications are used.

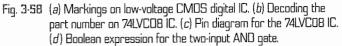

- Information on logic probe use in troubleshooting.

- A revised instruments section.

### Chapter 2

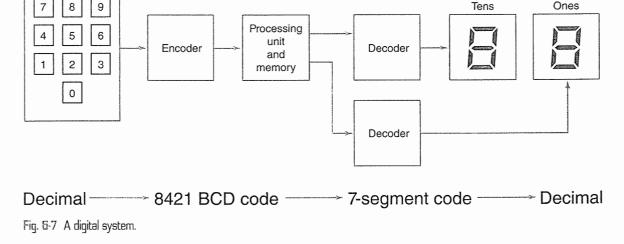

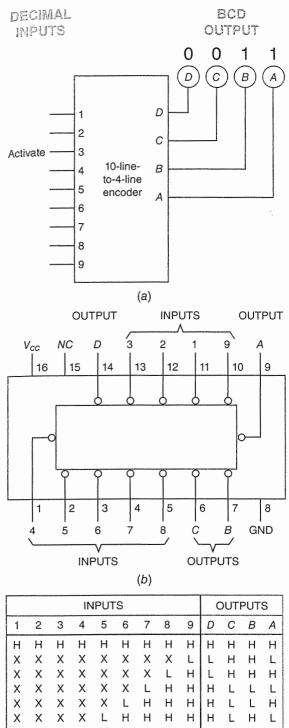

• Subsection on applications of encoders and decoders.

### Chapter 3

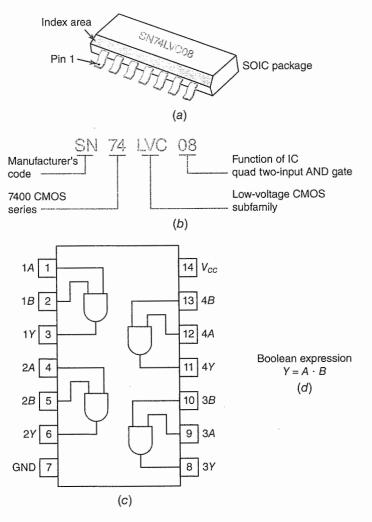

- Updated information on practical chips including lower voltage ICs.

- Expanded most self-test sections.

# Chapter 4

- Expanded several self-test sections.

- Revised material on data selectors.

### Chapter 5

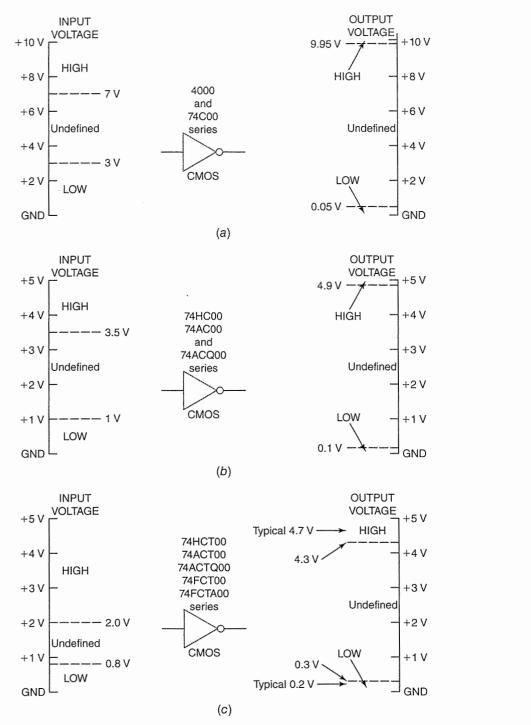

- Information on low-voltage ICs.

- Added many application assignments on interfacing.

# Chapter 6

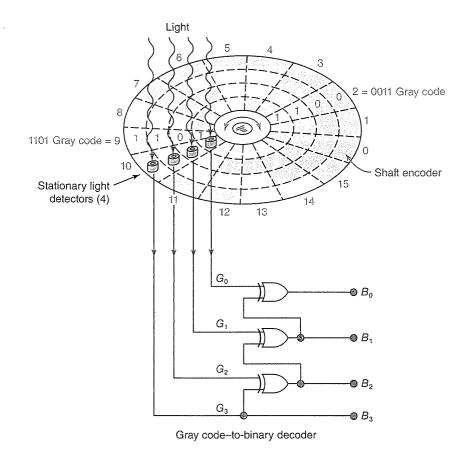

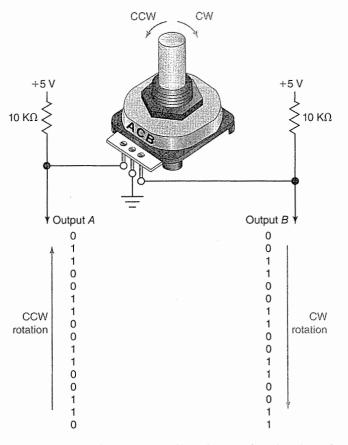

- Updated applications of the Gray code, including the shaft encoder, and new information on the quadrature encoder.

- Updated information on display technologies.

# Chapter 7

- Application of an R-S latch.

- A new detailed application of a latched encoderdecoder system.

### Chapter 8

• Expanded self-test questions.

# Chapter 10

- Expanded several self-tests.

- Updated binary subtraction section.

# Chapter 11

- Updated overview of memory section.

- Updated nonvolatile read/write memory section

- Updated memory packaging section.

- Expanded bulk storage section, including more information on USB flash drives.

- Internet research topics.

### Chapter 12

- Expanded self-test and critical thinking questions.

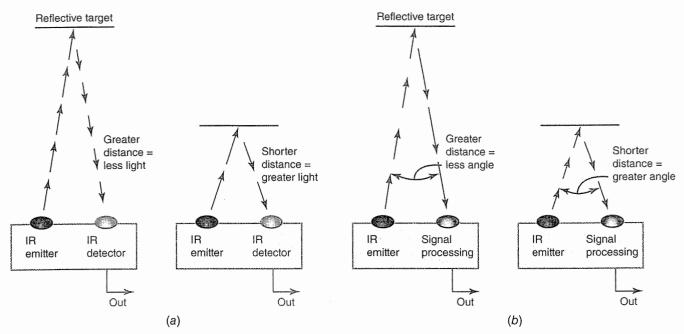

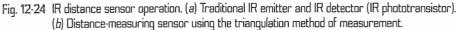

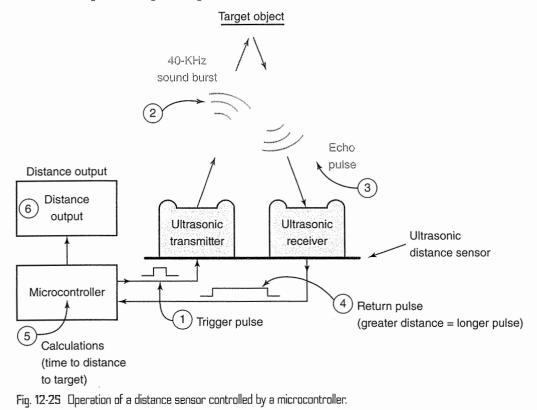

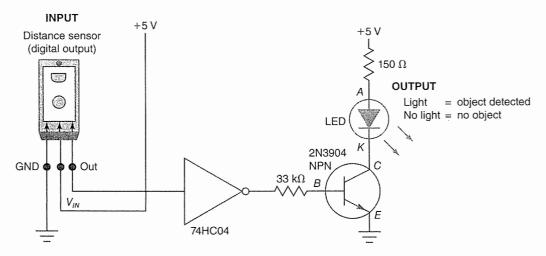

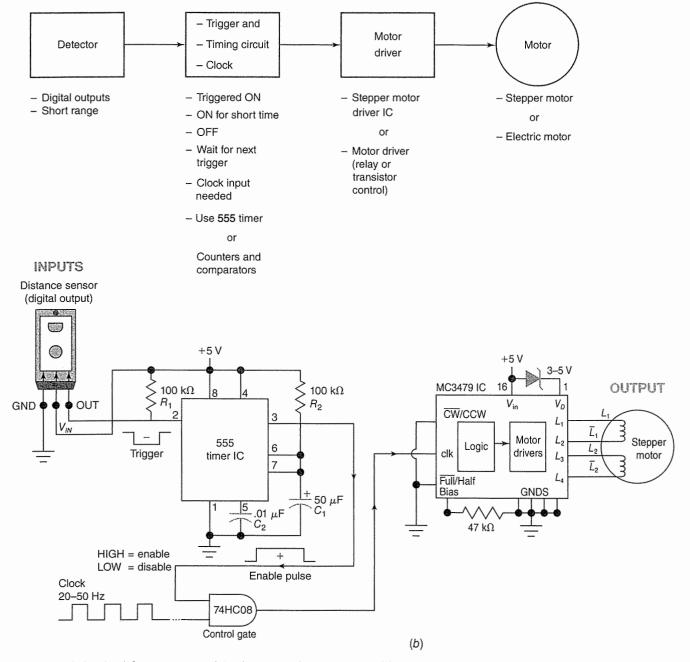

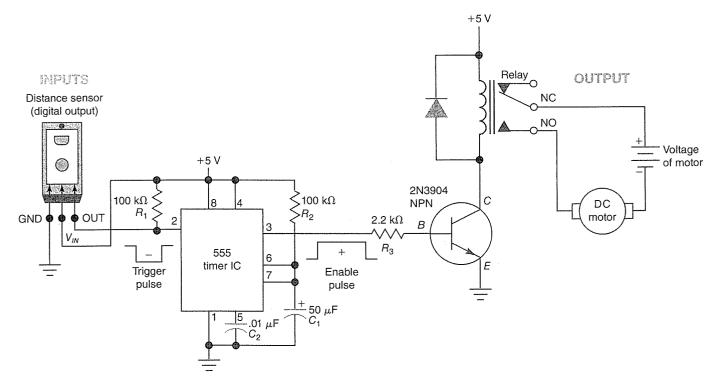

- Information on distance sensing with coverage of several sensor technologies.

- A DIY application demonstrating a distance sensor triggering the timed operation of a stepper motor.

# Chapter 13

- Updated microcomputer section.

- Updated data transmission section.

- A revised microcontrollers section.

- Application of a microcontroller with photo input and servo motor output.

# Chapter 14

• Expanded self-test questions.

# Additional Resources

An *Experiments Manual* for *Digital Electronics* contains a comprehensive test, a variety of hands-on lab exercises and experiments, and additional problems for each chapter in the textbook.

The Online Learning Center (OLC) at www.mhhe. com/tokheim8e includes comprehensive Multisim files, keyed to circuits found in the eighth edition, and a Multisim primer (written by Patrick Hoppe of Gateway Technical College), which provides a tutorial on the software for new users. The Multisim program itself is not included on the website, but the latest version, version 12, can be purchased through McGraw-Hill at a discount when you adopt this textbook. Visit **www.mhhe.com/tokheim8e** or contact your McGraw-Hill sales representative for more information.

The OLC also features chapter study resources, links to industry and association sites, and assignments and tests for students. Instructors can access the instructor side of the OLC to find a wide selection of information including:

- An Instructor's Manual that includes a list of the parts and equipment needed to perform lab experiments, learning outcomes for each chapter, answers to chapter review questions and problems, and more.

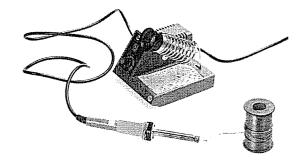

- PowerPoint presentations that correlate to all chapters and special PowerPoint presentations on breadboarding, soldering, circuit interrupters (GFCI and AFCI), and instrumentation.

- A test generator, EZ Test, which includes a test bank with questions for each chapter.

# Acknowledgments

Thanks to family members Marshall, Rachael, Dan, Jack, Ben and Carrie for their help on this project. I would also like to thank the reviewers who helped evaluate the textbook; I am grateful for their time and expertise.

Mike Carter Mercedes-Benz Institute

Richard Fornes Apollo Career Center Adult Education

J. C. Morrow Hopkinsville Community College

Tom Neal Southern Crescent Technical College

Randy Owens State Fair Community College Chrys Panayiotou Indian River State College

**G. Albert Popson** West Virginia Wesleyan College

Joseph Tront Virginia Tech

Mark Winans Central Texas College

Jillian Wooldridge Erie Institute of Technology

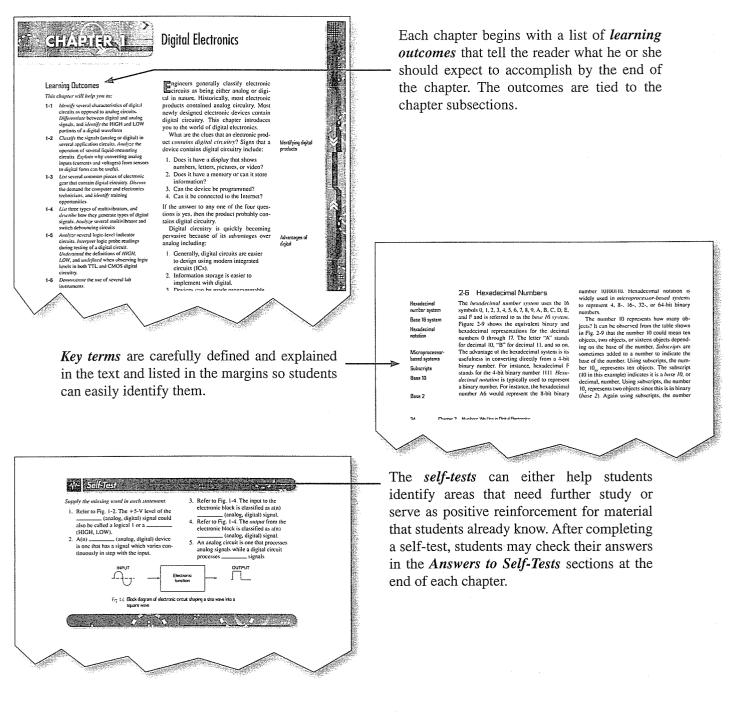

# Walkthrough

*Digital Electronics: Principles and Applications,* eighth edition, is designed for a first course in digital electronics. It provides a concise, modern, and practical approach that's suitable for a range of electricity and electronics

programs. With its easy-to-read style, numerous fullcolor illustrations, and accessible math level, the text is ideal for readers who need to learn the essentials of digital electronics and apply them to on-the-job situations.

# About the Author

Over several decades, Roger L. Tokheim has published many textbooks and lab manuals in the areas of digital electronics and microprocessors. His books have been translated into nine languages. He taught technical subjects including electronics for more than 35 years in public schools.

Electric and electronic circuits can be dangerous. Safe practices are necessary to prevent electrical shock, fires, explosions, mechanical damage, and injuries resulting from the improper use of tools.

Perhaps the greatest hazard is electrical shock. A current through the human body in excess of 10 milliamperes can paralyze the victim and make it impossible to let go of a "live" conductor or component. Ten milliamperes is a rather small amount of current flow: It is only *ten one-thousandths* of an ampere. An ordinary flashlight can provide more than 100 times that amount of current!

Flashlight cells and batteries are safe to handle because the resistance of human skin is normally high enough to keep the current flow very small. For example, touching an ordinary 1.5-V cell produces a current flow in the microampere range (a microampere is onemillionth of an ampere). The amount of current is too small to be noticed.

High voltage, one the other hand, can force enough current through the skin to produce a shock. If the current approaches 100 milliamperes or more, the shock can be fatal. Thus, the danger of shock increases with voltage. Those who work with high voltage must be properly trained and equipped.

When human skin is moist or cut, its resistance to the flow of electricity can drop drastically. When this happens, even moderate voltages may cause a serious shock. Experienced technicians know this, and they also know that so-called low-voltage equipment may have a highvoltage section or two. In other words, they do not practice two methods of working with circuits: one for high voltage and one for low voltage. They follow safe procedures at all times. They do not assume protective devices are working. They do not assume a circuit is off even though the switch is in the OFF position. They know the switch could be defective.

Even a low-voltage, high-current-capacity system like an automotive electrical system can be quite dangerous. Short-circuiting such a system with a ring or metal watchband can cause very severe burns especially when the ring or band welds to the points being shorted. As your knowledge and experience grow, you will learn many specific safe procedures for dealing with electricity and electronics. In the meantime:

- 1. Always follow procedures.

- 2. Use service manuals as often as possible. They often contain specific safety information. Read, and comply with, all appropriate material safety data sheets.

- 3. Investigate before you act.

- 4. When in doubt, *do not act*. Ask your instructor or supervisor.

# General Safety Rules for Electricity and Electronics

Safe practices will protect you and your fellow workers. Study the following rules. Discuss them with others, and ask your instructor about any you do not understand.

- 1. Do not work when you are tired or taking medicine that makes you drowsy.

- 2. Do not work in poor light.

- 3. Do not work in damp areas or with wet shoes or clothing.

- 4. Use approved tools, equipment, and protective devices.

- 5. Avoid wearing rings, bracelets, and similar metal items when working around exposed electric circuits.

- 6. Never assume that a circuit is off. Double-check it with an instrument that you are sure is operational.

- 7. Some situations require a "buddy system" to guarantee that power will not be turned on while a technician is still working on a circuit.

- Never tamper with or try to override safety devices such as an interlock (a type of switch that automatically removes power when a door is opened or a panel removed).

- 9. Keep tools and test equipment clean and in good working condition. Replace insulated probes and leads at the first sign of deterioration.

- 10. Some devices, such as capacitors, can store a *lethal* charge. They may store this charge for long periods

of time. You must be certain these devices are discharged before working around them.

11. Do not remove grounds and do note use adaptors that defeat the equipment ground.

i.

and the second second

Breezenser va

- 12. Use only an approved fire extinguisher for electrical and electronic equipment. Water can conduct electricity and may severely damage equipment. Carbon dioxide  $(CO_2)$  or halogenated-type extinguishers are usually preferred. Form-type extinguishers may also be desired in *some* cases. Commercial fire extinguishers are rated for the type of fires for which they are effective. Use only those rated for the proper working conditions.

- 13. Follow directions when using solvents and other chemicals. They may be toxic, flammable, or may damage certain materials such as plastics. Always read and follow the appropriate material safety data sheets.

- 14. A few materials used in electronic equipment are toxic. Examples include tantalum capacitors and beryllium oxide transistor cases. These devices should not be crushed or abraded, and you should wash your hands thoroughly after handling them. Other materials (such as heat shrink tubing) may produce

irritating fumes if overheated. Always read and follow the appropriate material safety data sheets.

- 15. Certain circuit components affect the safe performance of equipment and systems. Use only exact or approved replacement parts.

- 16. Use protective clothing and safety glasses when handling high-vacuum devices such as picture tubes and cathode-ray tubes.

- 17. Don't work on equipment before your know proper procedures and area aware of any potential safety hazards.

- 18. Many accidents have been caused by people rushing and cutting corners. Take the time required to protect yourself and others. Running, horseplay, and practical jokes are strictly forbidden in shops and laboratories.

- 19. Never look directly into light-emitting diodes or fiber-optic cables; some light sources, although invisible, can cause serious eye damage.

Circuits and equipment must be treated with respect. Learn how they work and the proper way of working on them. Always practice safety: your health and life depend on it.

Electronics workers use specialized safety knowledge.

XVI

# **Digital Electronics**

# Learning Outcomes

This chapter will help you to:

- 1-1 Identify several characteristics of digital circuits as opposed to analog circuits. Differentiate between digital and analog signals, and identify the HIGH and LOW portions of a digital waveform.

- **1-2** Classify the signals (analog or digital) in several application circuits. Analyze the operation of several liquid-measuring circuits. Explain why converting analog inputs (currents and voltages) from sensors to digital form can be useful.

- **1-3** *List* several common pieces of electronic gear that contain digital circuitry. *Discuss* the demand for computer and electronics technicians, and *identify* training opportunities.

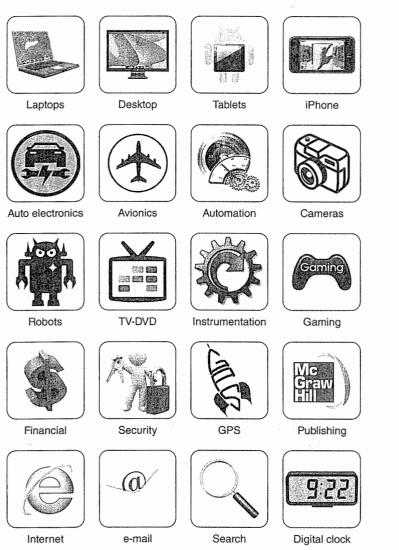

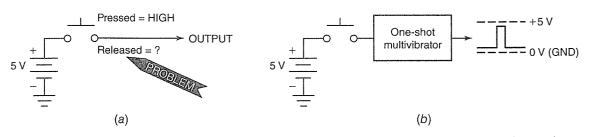

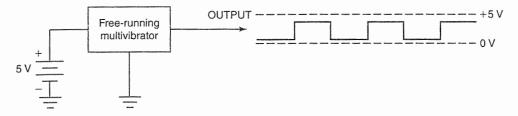

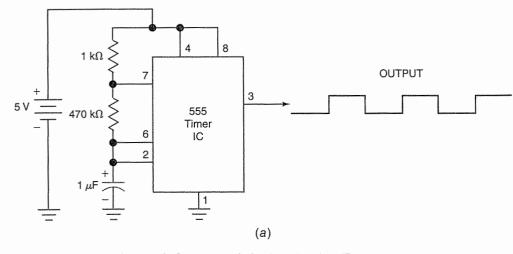

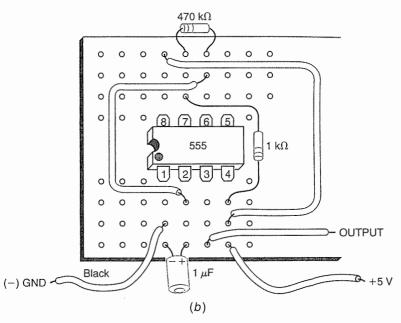

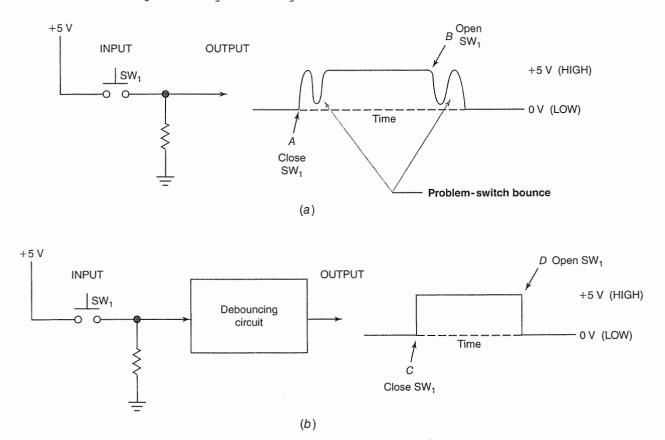

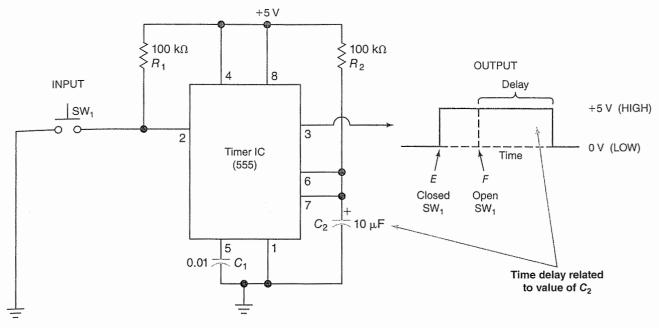

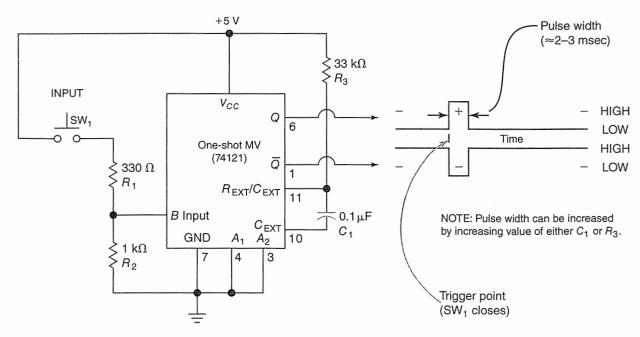

- **1-4** *List* three types of multivibrators, and *describe* how they generate types of digital signals. *Analyze* several multivibrator and switch debouncing circuits.

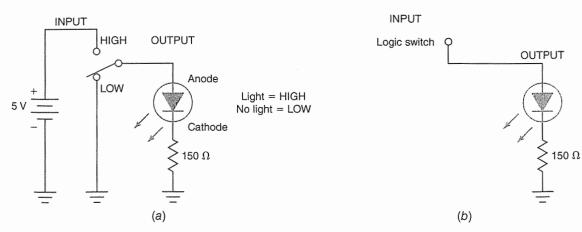

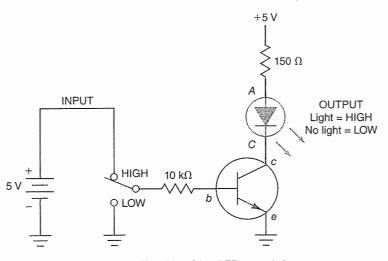

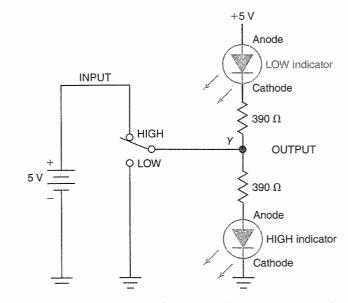

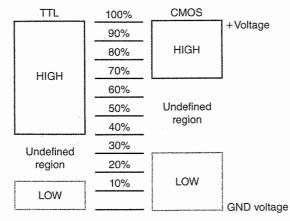

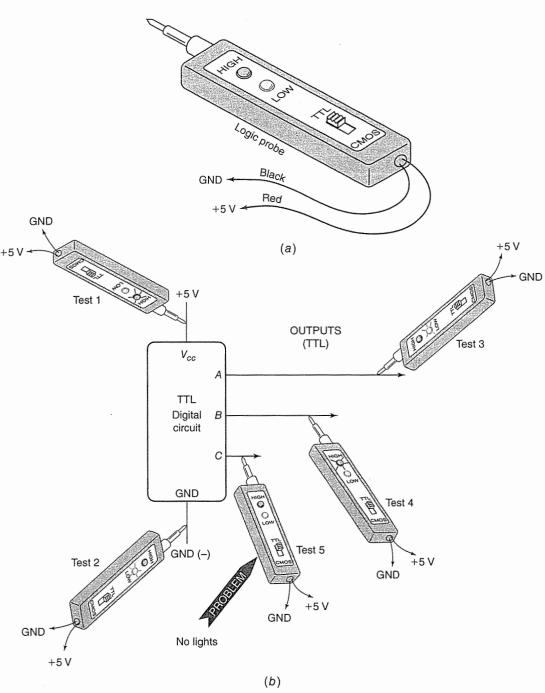

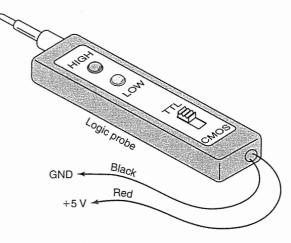

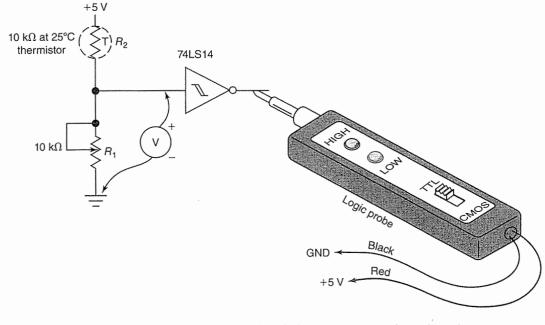

- 1-5 Analyze several logic-level indicator circuits. Interpret logic probe readings during testing of a digital circuit. Understand the definitions of HIGH, LOW, and undefined when observing logic levels in both TTL and CMOS digital circuitry.

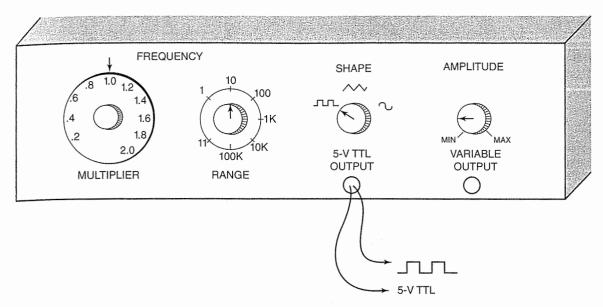

- **1-6** *Demonstrate* the use of several lab instruments.

ngineers generally classify electronic circuits as being either analog or digital in nature. Historically, most electronic products contained analog circuitry. Most newly designed electronic devices contain digital circuitry. This chapter introduces you to the world of digital electronics.

What are the clues that an electronic product *contains digital circuitry*? Signs that a device contains digital circuitry include:

- 1. Does it have a display that shows numbers, letters, pictures, or video?

- 2. Does it have a memory or can it store information?

- 3. Can the device be programmed?

- 4. Can it be connected to the Internet?

If the answer to any one of the four questions is yes, then the product probably contains digital circuitry.

Digital circuitry is quickly becoming pervasive because of its *advantages* over analog including:

- 1. Generally, digital circuits are easier to design using modern integrated circuits (ICs).

- 2. Information storage is easier to implement with digital.

- 3. Devices can be made programmable with digital.

- 4. More accuracy and precision are possible.

- 5. Digital circuitry is less affected by unwanted electrical interference called noise.

All persons working in electronics must have knowledge of digital electronic circuits. You will use simple integrated circuits and displays to demonstrate the principles of digital electronics. Identifying digital products

Advantages of digital

# 1-1 What Is a Digital Signal?

Analog signal

Volt-ohm-millimeter

HIGH and LOW

Digital multimeter

**Digital circuits**

signals

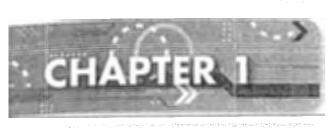

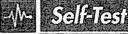

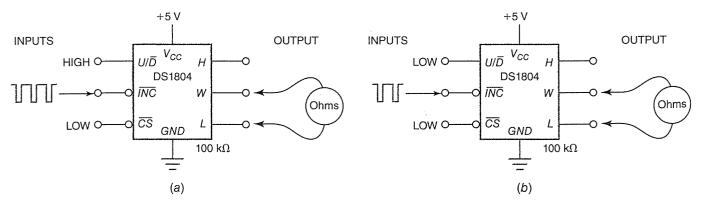

In your experience with electricity and electronics you have probably used analog circuits. The circuit in Fig. 1-1(a) puts out an analog signal or voltage. As the wiper on the potentiometer is moved upward, the voltage from points A to Bgradually increases. When the wiper is moved downward, the voltage gradually decreases from 5 to 0 volts (V). The waveform diagram in Fig. 1-1(b) is a graph of the analog output. On the left side the voltage from A to B is gradually increasing to 5 V; on the right side the voltage is gradually decreasing to 0 V. By stopping the potentiometer wiper at any midpoint, we can get an output voltage anywhere between 0 and 5 V. An analog device, then, is one that has a signal which varies continuously in step with the input.

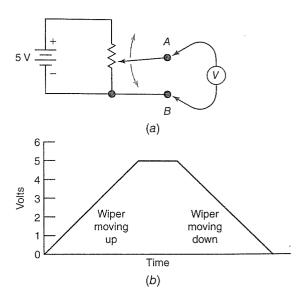

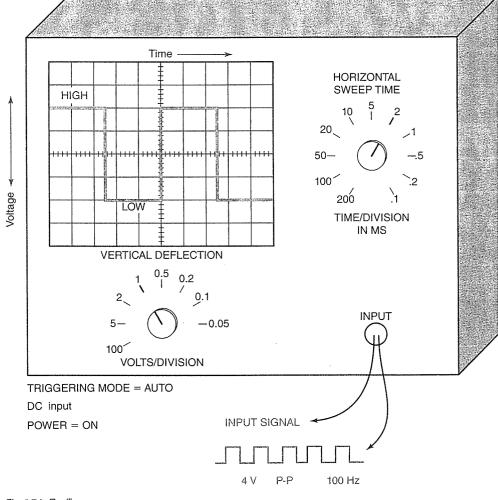

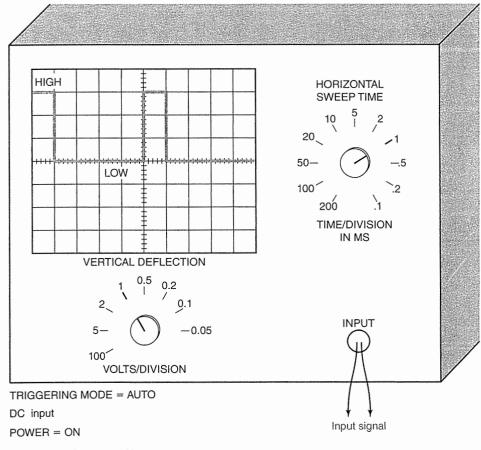

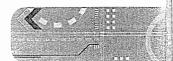

A digital device operates with a digital signal. Figure 1-2(a) pictures a square-wave generator. The generator produces a square waveform that is displayed on the oscilloscope. The digital signal is only at +5 V or at 0 V, as diagrammed in Fig. 1-2(b). The voltage at point A moves from 0 to 5 V. The voltage then stays at +5 V for a time. At point B the voltage drops immediately from +5 to 0 V. The voltage then stays at 0 V for a time. Only two voltages are present in a digital electronic circuit. In the waveform diagram in Fig. 1-2(b) these voltages are labeled HIGH and LOW. The HIGH voltage is +5 V; the LOW voltage is 0 V. Later we shall call the HIGH voltage (+5 V) a logical 1 and the LOW voltage (0 V) a logical 0. Circuits that handle only HIGH and LOW signals are called *digital* circuits.

The digital signal in Fig. 1-2(b) could also be generated by a simple on-off switch. A digital signal could also be generated by a transistor turning on and off. Digital electronic signals are usually generated and processed by integrated circuits (ICs).

Both analog and digital signals are represented in graph form in Figs. 1-1 and 1-2. A *signal* can be defined as useful information transmitted within, to, or from electronic circuits. Signals are commonly represented as a voltage varying with time, as they are in Figs. 1-1 and 1-2. However, a signal could be an electric current that either varies continuously (analog) or has an on-off (HIGH-LOW)

Fig. 1-1 (a) Analog output from a potentiometer. (b) Analog signal waveform.

characteristic (digital). Within most digital circuits, it is customary to represent signals in the voltage versus time format. When digital circuits are interfaced with nondigital devices such as lamps and motors, then the signal can be thought of as current versus time.

The standard volt-ohm-millimeter (VOM) shown in Fig. 1-3(a) is an example of an analog measuring device. As the voltage, resistance, or current being measured by the VOM increases, the needle gradually and continuously moves up the scale. A digital multimeter (DMM) is shown in Fig. 1-3(b). This is an example of a digital measuring device. As the

Fig. 1-2 (a) Digital signal displayed on scope. (b) Digital signal waveform.

(b)

Fig. 1-3 (a) Analog meter. (b) Digital multimeter (DMM). Courtesy Fluke Corporation. Reproduced with permission

current, resistance, or voltage being measured by the DMM increases, the display *jumps upward in small steps*. The DMM is an example of digital circuitry taking over tasks previously performed only by analog devices. This *trend toward digital circuitry* is growing. Currently, the modern technician's bench probably has both a VOM and a DMM.

Trend toward digital circuitry

M- Self-Test

Supply the missing word in each statement.

- Refer to Fig. 1-2. The +5-V level of the \_\_\_\_\_ (analog, digital) signal could also be called a logical 1 or a \_\_\_\_\_ (HIGH, LOW).

- 2. A(n) \_\_\_\_\_ (analog, digital) device is one that has a signal which varies continuously in step with the input.

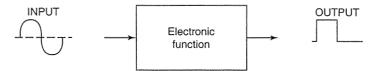

- Refer to Fig. 1-4. The *output* from the electronic block is classified as a(n)

\_\_\_\_\_ (analog, digital) signal.

- 5. An analog circuit is one that processes analog signals while a digital circuit processes \_\_\_\_\_\_\_\_\_\_ signals.

Fig. 1-4 Block diagram of electronic circuit shaping a sine wave into a square wave.

A photographic history of the computer. One of the first computers was the Eniac (*upper left*), developed in the 1940s. The 1970s marked the expanded use of the computer by businesses. The mainframe computer (*upper right*) was the tool of the time. In the 1980s personal computers such as the Apple lle (*lower left*) brought computers into our homes and schools. Today, personal computers can go anywhere, as laptop computers (*lower right*) increase in popularity.

# ABOUT ELECTRONICS

A Changing Field. Electronics is among the most exciting areas of technical study. New developments are reported weekly. Interestingly, most developments are based on the fundamentals learned in the first classes in electricity, analog and digital circuits, computer technology and robotics, and communications.

# 1-2 Why Use Digital Circuits?

Electronics designers and technicians must have a working knowledge of both analog and digital systems. The designer must decide if the system will use analog or digital techniques or a combination of both. The technicians must build a prototype or troubleshoot and repair digital, analog, and combined systems.

Analog electronic systems have been popular in the past. Older TVs, telephones, and automobiles featured analog circuits. Before modern digital computers, analog computers were used in some military applications such as fire control on ships.

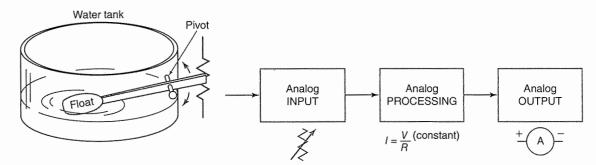

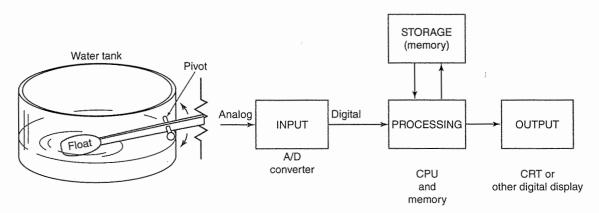

Most real-world information is *analog* in nature. Natural phenomena, such as time, temperature, humidity, wind speed, radiation, and sound intensity, are analog in nature. You probably have already measured voltage, current, resistance, power, capacitance, inductance, and frequency in other electricity and electronics courses. Other things to be measured include pressure, weight, oxygen (and other gases), ultrasonic sound, acceleration and tilt, vibration, direction (compass), global positioning, proximity, magnetic fields, linear distance, and angle of rotation (angular speed). They are all analog in nature. Engineers and technicians commonly use *sensors* to measure these things. Many sensors emit an analog signal.